# Composable and Predictable Power Management

## Composable and Predictable Power Management

## PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.Ch.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op donderdag 6 november 2014 om 12.30 uur

door

Andrew Thomas Nelson

Master of Science geboren te Craigavon, Verenigd Koninkrijk Dit proefschrift is goedgekeurd door de promotor: Prof. dr. Kees Goossens

Samenstelling promotiecommissie:

| Rector Magnificus       | voorzitter                                |

|-------------------------|-------------------------------------------|

| Prof. dr. Kees Goossens | Technische Universiteit Delft, promotor   |

| Dr. Anca Molnos         | CEA Leti, co-promotor                     |

| Prof. dr. Koen Bertels  | Technische Universiteit Delft             |

| Prof. dr. Ben Juurlink  | Technische Universität Berlin             |

| Prof. dr. Jose Pineda   | Technische Universiteit Eindhoven         |

| Dr. Said Hamdioui       | Technische Universiteit Delft             |

| Prof. dr. Henk Sips     | Technische Universiteit Delft, reservelid |

CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Andrew Thomas Nelson

Composable and Predictable Power Management Delft: TU Delft, Faculty of Elektrotechniek, Wiskunde en Informatica — III Thesis Technische Universiteit Delft. – With ref. –

Met samenvatting in het Nederlands.

ISBN 978-94-6186-366-9

Subject headings: Power Management, Real-Time, Embedded Systems.

*Cover image:* From a T-shirt design worn at DATE 2012, "The balance of power is shifting. Energy just declared indpendence".

#### Copyright © 2014 Andrew Thomas Nelson

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission from the author.

Printed in The Netherlands

## Acknowledgements

Trying to remember who all to thank is definitely a non-trivial part of the PhD. process. The research in this thesis has been carried out as part of a group effort to research composable and predictable System on Chips (SoCs) that we call CompSOC. I would therefore like to start by thanking my promoter Kees Goossens for not only providing guidance and encouragement throughout, but also for giving me the opportunity to be part of a group of like minded people who strive to keep applications from interfering in much the same way as some people obsessively try to prevent the different foods from touching on their plate. I also thank my co-promotor Anca Molnos for the many coffee fuelled discussions that helped ideas to form and new directions to be found.

At some point the talking has to end and the work just has to be done. Composable and predictable platforms, microkernels and operating systems do not just create themselves, and I would therefore like to thank everyone past and present who worked on the CompSOC platform, who are by now too numerous to start listing (but you know who you are). I would specifically like to thank Ashkan Beyranvand Nejad and Martijn Koedam, whom I collaborated with to create the Composable and Predictable Microkernel (CoMik) and the Predictable Operating System (POSe). Many thanks also go to the students who contributed work that assisted with my research, namely Sjoerd te Pas, Douwe van Nijnatten and Bas Vermaat.

Life is not all about work, and thankfully there has been some time to squeeze in fun in the past few years. In fact, it is hard to know where to begin with thanking all the people who helped me spend time away from behind a desk. Whether it is bar visits, Northern Ireland trips, weddings, Sinterklaas, cricket and sausage fests, or whatever, thanks again to Anca, Andreas, Ashkan, Bart, Benny, Björn, Davit, Elena, Eugenia, Golnoosh, Joyce, Jude, Karthik, Kees, Manil, Margriet, Martijn, Miran, Pao, Pavel, Radu, Richard, Sven, and the others who were accidentally omitted.

Thanks, to my family and Jo's family for their support and understanding during these last few years. Most of all, thanks to Jo for all the friendship and support she has given me during the highs and the lows of the last eleven years, of which the PhD. years must have been particularly trying of her patience. What am I going to be able to use as an excuse now?

## Abstract

## **Composable and Predictable Power Management**

The functionality of embedded systems is ever growing. The computational power of embedded systems is growing to match this demand, with embedded multiprocessor systems becoming more common. The limitations of embedded systems are not always related to chip size but are commonly due to energy and/or power constraints. While it can be possible to embed a more powerful Multiprocessor System on Chip (MPSoC), it is not always possible to provide an energy or power supply that meets its demands within the device's size and weight requirements. Power management through Dynamic Voltage and Frequency Scaling (DVFS) enables the device to be run at less than its maximum voltage and frequency, allowing high computational capability when necessary while conserving power at other times.

Embedded systems commonly perform real-time functionality. A real-time application has an associated formal model to verify that it meets its timing requirements. This formal model is used to perform a worst-case timing analysis to ensure that the application meets its requirements. These models incorporate the worst-case timing of the application's computation and communication. Timing changes due to power management must also be taken into account, complicating the verification process.

The drive for evermore functionality has led to mixed time-criticality systems, in which multiple applications of various timing criticalities share the same (hardware) resources. This complicates the verification process further as the timing interference due to shared resource contention must be taken into account. A monolithic verification effort is therefore traditionally required after system integration and must be carried out again if any modifications are made that affect the timing of any of the applications.

The problem that we aim to solve in this work is to *enable real-time applications to perform independent execution and power management without violating their timing requirements or invalidating the timing verification of concurrently executing applications.*

To solve this problem, we contribute the Composable and Predictable Microkernel (CoMik) to composably and predictably virtualise processors. When used in combination with composable and predictable memory controllers and interconnect (as provided by the Composable and Predictable System-on-Chip (CompSOC) platform), these virtual processors cannot interfere with each other's timing by even a single cycle. If whatever executes on the virtual processors (e.g. an Operating System (OS) or an application directly) has a real-time requirement, it can be verified independently of whatever executes on the concurrent virtual processors and other virtual resources.

To enable formally analysable application execution, we contribute the Predictable Operating System (POSe) that enables dataflow applications to be executed on the (virtualised) processor. We contribute a combined application and platform dataflow graph, including an algorithm to automate this process. When annotated with worst-case timings, the combined application and system graph is then used to verify that the application meets its timing requirement.

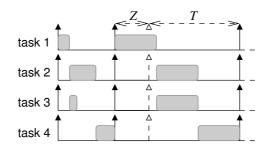

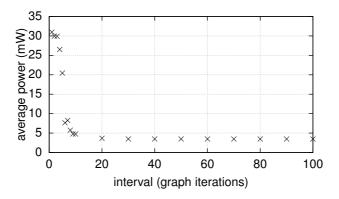

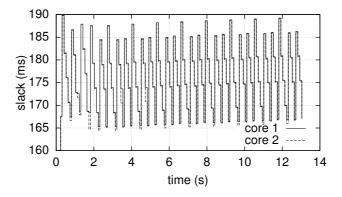

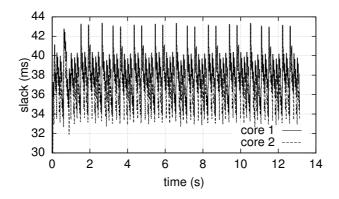

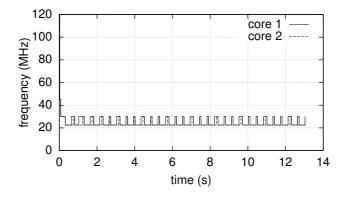

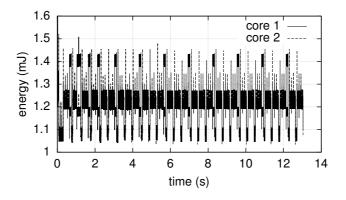

If the application's performance is better than its requirement (e.g. when the input or platform behaviour are better than worst case), its performance can be reduced using DVFS to achieve a reduction in power consumption. We contribute an off-line convex optimisation that uses the combined application and platform dataflow model to derive static run-time operating frequency levels to achieve low power consumption. The off-line technique is able to exploit static slack in the schedule, but not dynamic run-time slack due to variations in task execution times. Before dynamic slack can be used it must be possible to observe it. For this purpose, CoMik provides independent power, energy and timing accounting per virtual processor. This enables each virtual processor to be assigned individual power and energy budgets and POSe applications to be assigned timing budgets. We contribute a description and model of how energy and power budgets can be distributed between multiple virtual processors, enabling whatever executes on the virtual processor to perform composable independent power-management without affecting the ability of other virtual processors from using their entire budget allocation.

Using CoMik's accounting infrastructure, we also demonstrate how the quality of applications can be dynamically scaled to assist meeting timing, energy or power requirements. We further contribute a distributed dynamic power management policy that enables dataflow applications that are mapped onto multiple (virtual) processors to make distributed dynamic slack observations and local power-management decisions.

We demonstrate the applicability of the presented techniques on an implemented Field Programmable Gate Array (FPGA) prototype of a CompSOC hardware platform instance, using an H.263 decoder as a case-study application. We show that our techniques do not only work in theory, but that they are also implementable and implemented.

## Contents

| 1 | Intr | oduction                                         | 1  |

|---|------|--------------------------------------------------|----|

|   | 1.1  | Consumer Trends                                  | 2  |

|   | 1.2  | Industry Trends                                  | 2  |

|   | 1.3  | Problem Statement                                | 5  |

|   | 1.4  | Requirements                                     | 5  |

|   | 1.5  | Contributions                                    | 7  |

|   | 1.6  | Overview                                         | 10 |

| 2 | The  | CompSOC: Mixed Time-Criticality Platform         | 11 |

|   | 2.1  | Real-time Dataflow Applications                  | 14 |

|   | 2.2  | CompSOC: Predictable and Composable Hardware     | 22 |

|   | 2.3  | CoMik: Predictable and Composable Virtualisation | 39 |

|   | 2.4  | POSe: Dataflow Execution Library                 | 51 |

|   | 2.5  | Dataflow Modelling of Application and Platform   | 56 |

|   | 2.6  | Related Work                                     | 63 |

|   | 2.7  | Summary                                          | 64 |

| 3 | Con  | posable Time, Energy and Power Accounting        | 67 |

|   | 3.1  | DVFS Power Model                                 | 67 |

|   | 3.2  | POSe Accounting                                  | 72 |

|   | 3.3  | CoMik Composable Accounting                      | 74 |

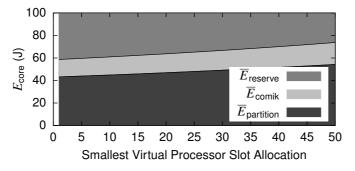

|   | 3.4  | Composable Energy Budget Distribution            | 77 |

|   | 3.5  | Related Work                                     | 89 |

|   | 3.6  | Summary                                          | 90 |

| 4   | Stati                                  | c Voltage and Frequency Scaling                  | 91  |  |  |

|-----|----------------------------------------|--------------------------------------------------|-----|--|--|

|     | 4.1                                    | Convex Power Optimisation                        | 92  |  |  |

|     | 4.2                                    | Formulation for CVX convex solver                | 95  |  |  |

|     | 4.3                                    | Applied in Practice                              | 98  |  |  |

|     | 4.4                                    | Related Work                                     | 101 |  |  |

|     | 4.5                                    | Summary                                          | 101 |  |  |

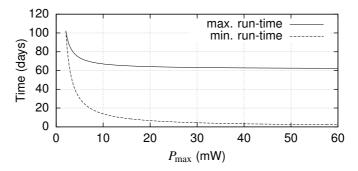

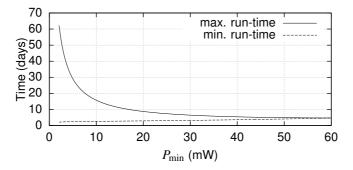

| 5   | Dyna                                   | amic Voltage and Frequency Scaling               | 103 |  |  |

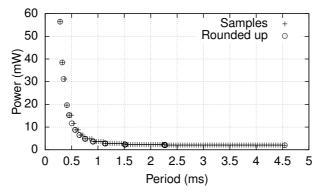

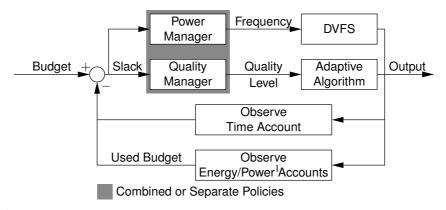

|     | 5.1                                    | Quality/Power Trade-off Mechanism                | 105 |  |  |

|     | 5.2                                    | Distributed Real-time Multi-Core DVFS            | 121 |  |  |

|     | 5.3                                    | Distributed Power Management Applied in Practice | 131 |  |  |

|     | 5.4                                    | Related Work                                     | 136 |  |  |

|     | 5.5                                    | Summary                                          | 139 |  |  |

| 6   | Case                                   | Study                                            | 141 |  |  |

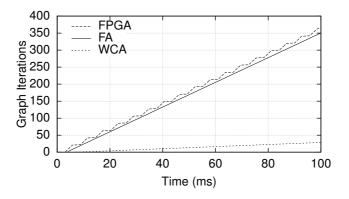

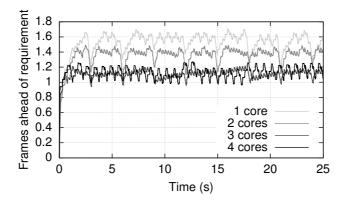

|     | 6.1                                    | CoMik's Composable Virtualisation in Action      | 143 |  |  |

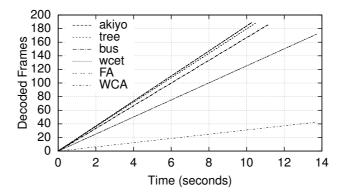

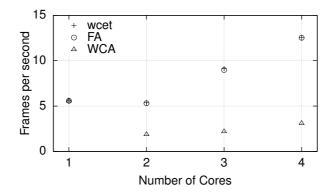

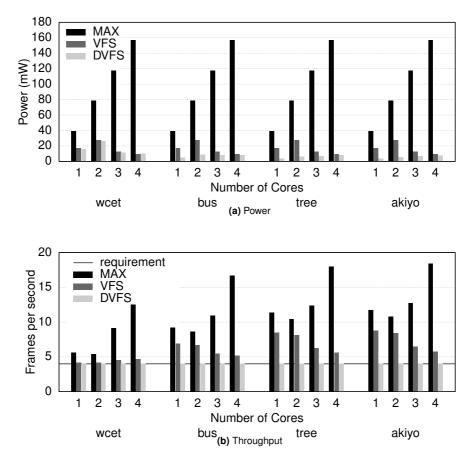

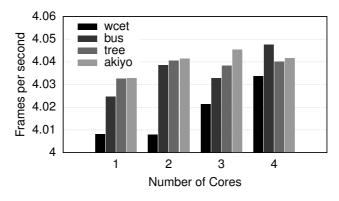

|     | 6.2                                    | CompSOC HSDF Model Evaluation                    | 144 |  |  |

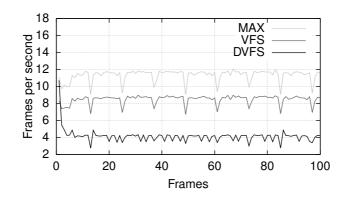

|     | 6.3                                    | Power Management of an H.263 Decoder             | 150 |  |  |

|     | 6.4                                    | Summary                                          | 155 |  |  |

| 7   | Conclusions and Future Work            |                                                  |     |  |  |

| Bil | oliogr                                 | aphy                                             | 170 |  |  |

| A   | Glos                                   | sary                                             | 171 |  |  |

|     | A.1                                    | Abbreviations                                    | 171 |  |  |

|     | A.2                                    | Lists of Symbols                                 | 174 |  |  |

| B   | Exai                                   | nple CoMik and POSe Application Configuration    | 177 |  |  |

| С   | C Example HSDFG Convex Analysis Script |                                                  |     |  |  |

| D   | Curi                                   | riculum Vitae                                    | 185 |  |  |

| Е   | E Publications 1                       |                                                  |     |  |  |

| F   | Samenvatting 1                         |                                                  |     |  |  |

х

# CHAPTER

## Introduction

Embedded systems are now ubiquitous in everyday life. This is in part due to the omnipresent nature of technology that keeps us permanently tethered to the internet, such as mobile phones and tablet computers. Other uses of embedded technology are not always as obvious to the end user, e.g. by reducing usage complexity or increasing functionality of existing everyday objects, such as cars and washing machines. In these roles, it is typically used to perform real-time tasks that interact with the physical environment, e.g. fuel injection regulation in modern combustion engines. Whatever the role of the embedded system, the end user usually does not want to have to think much about it, or even know that it is there at all. To quote ubiquitous computing pioneer Mark Weiser [106]:

## 'The most profound technologies are those that disappear. They weave themselves into the fabric of everyday life until they are indistinguishable from it.'

While much has changed since 1991, many of the predictions contained in [106] came to fruition, and this quote is still as relevant today as when it was made.

Even though embedded systems are ubiquitous, it does not mean that there are no outstanding problems to solve. Everyone with a smartphone will be aware that one of the unpleasant consequences of this particular piece of technology "weaving" itself into our everyday lives, is the need for us to monitor and tend to its energy needs by plugging it in and recharging it all too frequently. We therefore proceed in this section to investigate the consumer and industrial trends that led to this research into composable and predictable power management.

## **1.1 Consumer Trends**

Demand for portable devices, such as smartphones and tablets, is increasing [93, 113]. These devices require a portable power source, which is commonly a battery that needs the user to plug it in to recharge it. Intervals between charges depend on both the capacity of the battery and rate at which the device consumes energy from the battery, i.e. its power consumption. Figure 1.1 presents the "Top 10 Smartphone Purchase Drivers" resulting from a recent consumer survey carried out by market research company IDC. This survey shows that battery life is the main purchase driver across all major smartphone operating systems. [It also indicates that weight/size is less of a concern so maybe manufacturers should think about increasing the battery capacity by putting in a larger battery.]

It is looking increasingly likely that smartphones and tablets are just the tip of the portable device iceberg. Consumer trend watchers are highlighting the rising trend of wearable devices as one of the major trends of 2014 [3,56]. As an example, not content with the information relaying capability of their smartphone, consumers are expected to also want another smaller device on their wrist in the form of a smartwatch, which is inevitably another device that needs to be charged regularly.

Wearable devices form part of a larger embedded system trend called the "internet of things" [42, 57]. With Wireless Local Area Networks (WLANs) in almost every home, more and more consumer devices are being embedded with some form of internet connectivity, creating an internet of things. This is leading to another consumer trend in 2014 called "the internet of caring things". These are portable devices and sensors that perform a caring role, e.g. remote patient monitoring.

In summary, consumer trends are towards smarter connected portable devices. The smartphone is one such device that has been on the market for a number of years and a recent consumer survey presented in Figure 1.1 shows that battery life is a key concern when deciding which smartphone to purchase.

## **1.2 Industry Trends**

Consumer demands for smarter devices have not gone unnoticed by various industries. For example, the automotive industry is increasingly catering for consumer gadget addictions [102]. The most interesting of these for the future direction of the automotive industry are the in-car gadgets that are automating the driving process, such as automated parking, with fully automated driving being the end goal [74].

Automation is practical for both ease of use and safety, but the demand for ever greater functionality has led to mixed criticality systems [21]. Mixed criticality generally refers to mixing applications with differing safety criticalities on the same hardware

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Android vs. | iOS vs. \ | Vindows |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|---------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>N</b> 5  | ×5"       | Ð       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |           |         |

| Battery Life                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56%         | 49%       | 53%     |

| Ease of Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33%         | 39%       | 38%     |

| webOS Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37%         | 32%       | 40%     |

| Touch Screen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34%         | 34%       | 37%     |

| Screen Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37%         | 22%       | 34%     |

| (((•)))<br>Type of Network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27%         | 30%       | 20%     |

| BROAM POT CONTRACT OF CONTRACT | 25%         | 32%       | 25%     |

| Weight/Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25%         | 21%       | 24%     |

| Camera resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25%         | 19%       | 23%     |

| Web Browsing Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23%         | 22%       | 22%     |

**Figure 1.1:** Smartphone purchase drivers. (*Source: IDC's ConsumerScape360, by Michael DeHart; via: Twitter, Francisco Jeronimo, http://t.co/AS2VjrEF2x, 12th May 2014*)

platform. Reduced area, weight, power and cost of materials are all reasons to share hardware resources between applications, but potential interference due to resource sharing complicates the verification of safety critical applications. For example, uncharacterised non safety critical applications that share the same resources as a safety critical real-time application could cause unbounded timing interference on the shared resources making it impossible to guarantee the safety critical application's timing behaviour.

In this thesis, we focus on the particular problem of mixed time-criticality that forms part of the larger problem of mixed criticality in general. Real-time applications have either soft, firm or hard timing requirements, ranging from lowest to highest strictness of the requirement [14]. Safety critical real-time applications have hard timing requirements [22], as failure to meet the requirement may cause physical harm to the system and its surroundings, e.g. an electronic braking system. Firm real-time applications have strict timing requirements with the value of the application's output deteriorating rapidly after the requirement deadline, but do not pose a risk of physical harm, e.g. a software defined radio. Soft real-time applications have timing requirements but the value of the output does not deteriorate so rapidly after a missed deadline and can therefore be deemed functional while occasionally missing deadlines, e.g. an MP3 decoder. Non real-time applications are applications of various timing requirement. In a mixed time-criticality system, applications of various timing requirements share the same platform resources.

Multi-core platforms compound the problem of verifying real-time applications in a mixed time-criticality system further, as applications can be mapped across multiple processors sharing not only the processors but also the interconnect that enables the processors to communicate. Temporal isolation is a simplification strategy that allows concurrent applications to execute on shared resources with statically bounded interference [75]. The timing of applications can therefore be verified in isolation as the worst-case interference is known in advance.

Virtualisation has been used for many years in desktop and server machines to share resources, and is becoming increasingly common for embedded systems [45, 46]. Virtualisation simplifies resource sharing by enabling applications and Operating Systems (OSs) to execute on virtual machines as if they were being executed on a physical hardware platforms, simplifying the programming/porting process. Combining virtualisation with temporal isolation creates virtual machines that are temporally isolated from each other. Real-time applications can therefore be mapped onto a virtual machine and verified independently from concurrent applications.

Power management of embedded systems enables applications to reduce the power consumption of the platform by performing Dynamic Voltage and Frequency Scaling (DVFS) or temporarily shutting down parts of the platform [15]. A reduction in power consumption is achieved in exchange for an increase in computation time. This complicates providing timing guarantees for real-time applications as the timing behaviour of the application depends on used DVFS levels. While much work has been carried out on power management of real-time systems [7,47,112], the power management of mixed time-criticality systems is still an open issue. This is also the case for embedded virtualisation. While power management for virtual platforms is suggested in [46] for the context of migrating virtual machines off of a core to shut it down, performing virtualised power management using DVFS is unresolved.

In summary, there is a continuing trend for more functionality provided by embedded systems. Resource sharing enables functionality to be added at lower cost than additional dedicated hardware. This leads to an increase in mixed time-criticality systems. Temporal isolation simplifies the verification of real-time applications on shared resources while virtualisation simplifies programming shared resources. Power management of mixed time-criticality platforms and independent DVFS in virtual platforms are still open issues.

## **1.3** Problem Statement

Power management of applications running on embedded systems is important due to design considerations and consumer demands. These two factors are also driving the creation of mixed time-criticality systems. Verifying the timing behaviour of real-time applications in these systems is non-trivial, due to the possibility of inter-application timing interference. As power management through DVFS changes application timing, verifying application timing and bounding/limiting its effects on concurrent applications is a problem.

The problem that we aim to solve in this work is therefore to *enable real-time applications to perform independent execution and power management without violating their timing requirements or invalidating the timing verification of concurrently executing applications.*

## **1.4 Requirements**

Given our problem statement, we break our proposed solution down into the topics of:

- **Composability:** The ability to share resources within strict budgets such that a system can be composed of independently executing and verifiable applications on Virtual Platforms (VPs).

- Predictability: The ability to abstract a VP to a formal model to predict behaviours.

- Low Power: To enable applications to reduce their power consumption.

We introduce these topics in the following sections.

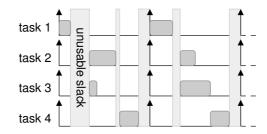

## **1.4.1** Composability

Composability enables concurrent applications to share resources within set limitations/budgets. For timing, composability is sometimes referred to as temporal isolation. In this thesis, we refer to the strictest form of composability where budgets for time, space and energy resources are strictly enforced, e.g. when time sharing a memory resource using Time Division Multiplexed (TDM) arbitration, each composable virtual processor gets a time allocation in the schedule and a space allocation (dedicated memory region), with the boundaries of that allocation being strictly enforced so that each thread can only use its allocated time/space and no more than that. By composably arbitrating all shared resources using (statically allocated) predictable budgets per composable thread, applications are cycle-accurately temporally isolated, i.e. they cannot interfere with each other's timing behaviour by even a single cycle.

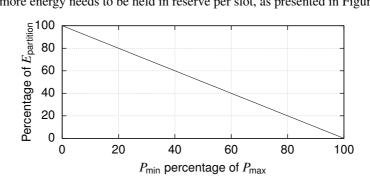

The energy/power supply of an embedded system is also typically a shared resource, i.e. a battery. Our problem statement calls for independent power management and hence also composable sharing of the energy/power resource. Applying the same principles as temporal composability, each application must receive a statically allocated strictly enforced energy/power budget. Each application must be able to use this budget in its entirety, regardless of the behaviour of concurrent applications.

#### 1.4.2 Predictability

Predictability is essential to give timing guarantees for real-time applications. We consider an application to be predictable if a formal abstraction can be created that can be used to derive predictions about the application's timing behaviour prior to execution. The accuracy of the formal model is determined by how close the predictions are to reality. For real-time applications, it is important that the model is not only accurate but also temporally conservative, i.e. that the timing of the application in reality can only be equal to or better than the prediction by the model.

For an application to be predictable it must be executed on a predictable hardware platform. It must therefore be possible to formally model the behaviour of the hardware on which the application executes. On a multi-core memory mapped platform with distributed shared memory, this means that it must be possible to conservatively model the application's execution on the processors and accesses to and from local and remote shared memories. The user- and system-software, processors, interconnect, memory controllers, memories and any other peripherals that the application might interact with must therefore all have deterministic timing bounds. The composable arbitration of resources must also be carried out in a deterministic manner so that it can be formally modelled.

### 1.4.3 Low Power

The purpose of power management is to reduce power and/or energy consumption. DVFS is a common mechanism that enables a (usually) monotonic trade-off in performance for a reduction in power consumption, i.e. a computation can be performed with lower power consumption, but the computation will take longer. To be able to use the DVFS mechanism while providing timing guarantees for real-time applications, it must therefore

#### 1.5. CONTRIBUTIONS

be possible to incorporate the timing effects of the DVFS mechanism into the application's timing formalism.

Given our problem statement, multiple applications can share the processor. The interference caused by each application's power management strategy on the other applications must therefore be bounded and modelled as part of the timing formalism of the applications. This is not practical, as the bounds on the interference of all other concurrent applications would have to be known at design time. Using our strict definition of composability, applications know their budget allocation at design time that this budget is guaranteed to be interference free.

To achieve this, not only the arbitration of the DVFS mechanism must be composable, but also its effects. This means that a DVFS level set by one application cannot interfere with or be altered by other applications. The effects of DVFS also concern energy/power budget depletion rate. Energy and power budgets allocated to applications must also be guaranteed and strictly enforced, meaning that budgets must be able to be used in their entirety, regardless of the behaviour of other applications.

## **1.5** Contributions

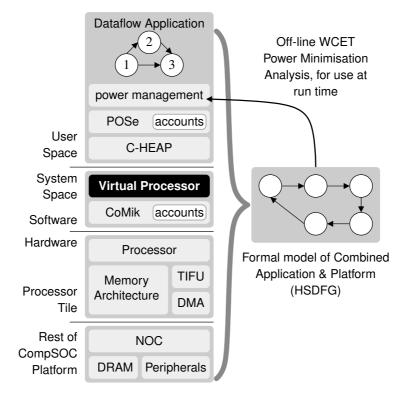

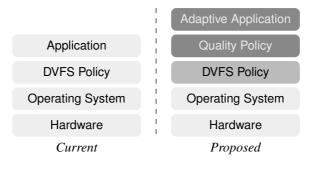

We proceed to outline the set of contributions made by this thesis that meet the requirements of our problem statement. Figure 1.2 presents a high level overview of our proposed solution to the problem statement in Section 1.3.

## 1.5.1 Architecture

To enable composable and predictable execution of applications, we contribute the following to our Composable and Predictable System-on-Chip (CompSOC) platform's software stack:

- The Predictable Operating System (POSe) OS implements the dataflow Model of Execution (MOE) enabling applications to be structured, executed and analysed as dataflow graphs.

- The Composable and Predictable Microkernel (CoMik) microkernel<sup>1</sup> composably and predictably virtualises a physical processor into multiple virtual processors, enabling cycle-accurate composable sharing of the physical processor.

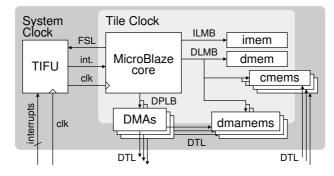

We contribute the following hardware to enable the CompSOC platform's composable and predictable software stack:

• Composable processing tile memory architectures. We propose multiple memory architectures that enable temporally composable sharing of local scratch pad memories with Direct Memory Access (DMA) support.

<sup>&</sup>lt;sup>1</sup>The work on CoMik was carried out in collaboration with Ashkan Beyranvand Nejad [16].

Figure 1.2: Composable power management for real-time dataflow applications.

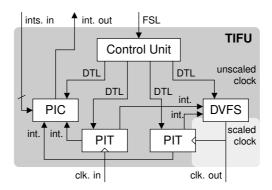

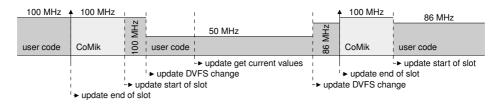

• The Timer-centric Interrupt and Frequency Unit (TIFU)<sup>1</sup> is a hardware module that each processor tile has. It is used to coordinate interrupt and DVFS changes at programmable times. This module assists CoMik to provide virtualised interrupts and DVFS configuration, enabling each virtual processor to have an independent DVFS level.

## 1.5.2 Power Management

To achieve our objective of independent power management for real-time applications, we contribute the following

• A method to allocate composable per application energy/power budgets, such that each application can use its entire allocated budget regardless of the behaviours of other applications.

<sup>&</sup>lt;sup>1</sup>The work on the TIFU was carried out in collaboration with Ashkan Beyranvand Nejad [16].

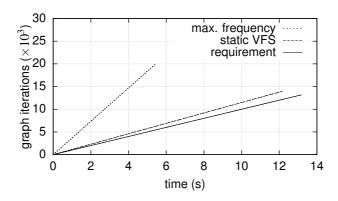

- An analysis method to derive low-power conservative static Voltage and Frequency Scaling (VFS) levels for real-time dataflow applications executing on the CompSOC platform.

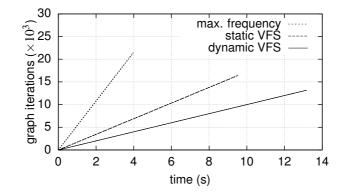

- An analysis method to derive low-power conservative DVFS levels that are selected at run-time using a distributed closed control loop, for real-time dataflow applications executing on the CompSOC platform.

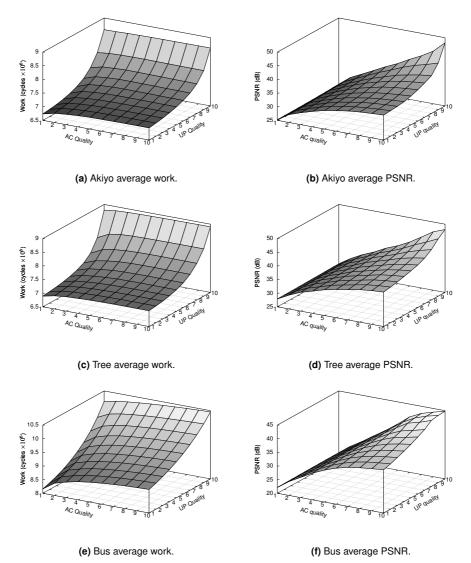

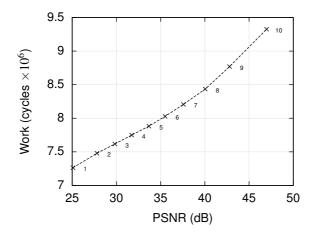

- An investigation into the use of quality scaling mechanisms in adaptive applications to assist run-time power management by trading a reduction in quality for a reduction in execution time. We carry out this investigation for an adaptive H.263 decoder application.

- A case study analysis of our static and dynamic power management techniques applied to an H.263 decoder.

## 1.5.3 Formalism

To be able to provide real-time guarantees, and therefore to also perform DVFS while guaranteeing not to violate requirements, we contribute the following:

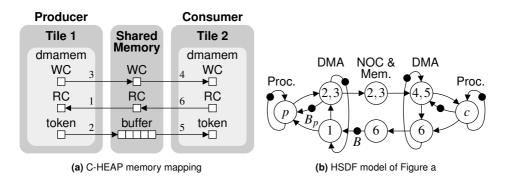

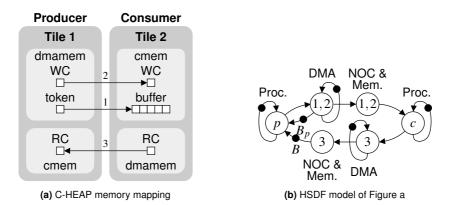

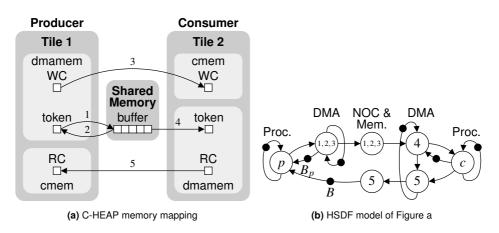

- Dataflow timing abstractions for multiple inter-core First In First Out (FIFO) configurations, using the C-HEAP communication protocol.

- A method to generate combined application and platform Homogeneous Synchronous Dataflow Graphs (HSDFGs) that can be used for worst case analysis when the actors are annotated with their Worst-Case Execution Times (WCETs).

## 1.5.4 Summary

As illustrated in Figure 1.2, our contributions enable real-time dataflow applications to execute on composably virtualised hardware, including energy and power budgets, e.g. a virtualised battery. This enables each dataflow application to be independently formally modelled as a combined application and CompSOC platform HSDFG. These independent models enable worst case timing analysis of the application when actors are annotated with WCETs making them suitable for deriving timing guarantees for real-time applications. We use the application's formal model to derive suitable low-power DVFS levels that are guaranteed not to violate the application's real-time requirement. We contribute two power management techniques. One of our techniques derives static conservative VFS levels. Our other technique derives a set of conservative DVFS points that depend on application progress using a run-time power management closed control loop to monitor the application's progress and select an appropriate conservative DVFS operating point. We demonstrate our power management techniques applied to an implementation of an H.263 decoder on an Field Programmable Gate Array (FPGA) prototyped instance of the CompSOC platform.

## 1.6 Overview

The remainder of this thesis is organised as follows. We present details of the composable and predictable CompSOC platform in Chapter 2. We describe the hardware platform together with the dataflow formalism that we use to abstract the platform's timing. We conclude Chapter 2 by describing how the application and CompSOC hardware platform can be modelled together as an HSDFG. In Chapter 3, we give an overview of the power model we use to account for processor power consumption on an FPGA prototyped implementation of the CompSOC platform. We also describe how energy, power and time are composably accounted for using CoMik and POSe. This also includes a description of how energy/power budgets are composably allocated in the CompSOC platform, so that they can be used in their entirety regardless of the behaviour of concurrent applications.

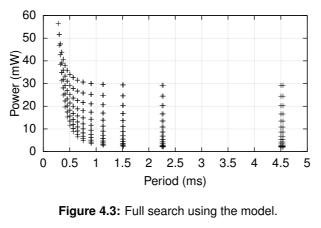

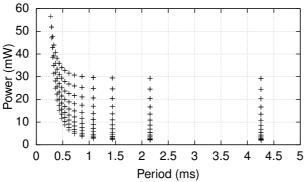

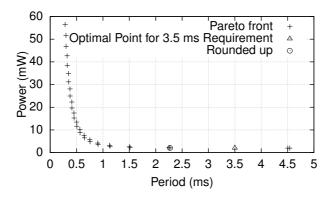

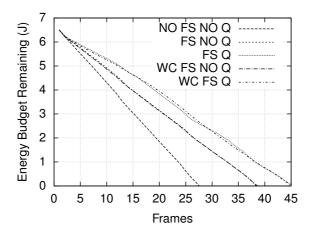

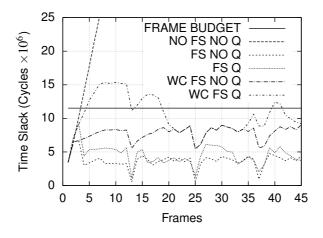

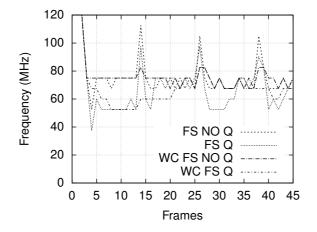

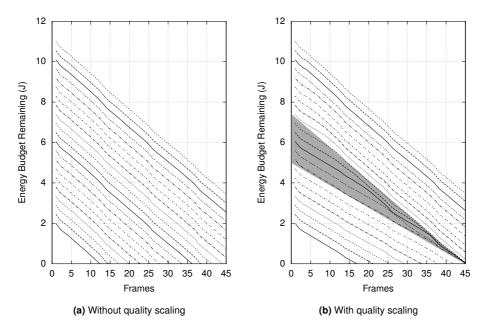

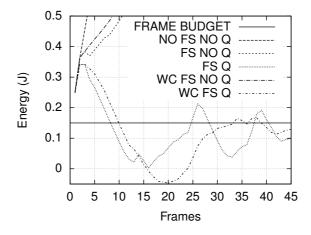

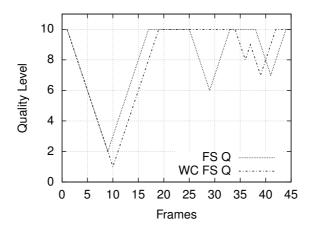

We proceed in Chapter 4 to propose an off-line power management method to derive low power DVFS levels per core for a real-time dataflow application. The derived DVFS levels are guaranteed not to violate the application's timing requirements. The method we propose in Chapter 4 cannot make use of dynamic variations in task execution time. In Chapter 5, we therefore propose a run-time power management method that makes use of dynamic variations in task execution time to lower the power consumption of the application further than achievable with our static power management technique. We also investigate the use of quality scaling mechanisms in adaptive applications to trade a decrease in quality for a decrease in execution time, thereby enabling further reductions to the power consumption.

Having described our methods in the previous chapters, we apply them to an H.263 video decoder application in Chapter 6. We show that our power management techniques are not only theoretical, but can be implemented in practice using an FPGA prototyped CompSOC platform. We bring this thesis to an end in Chapter 7, by making conclusions about the work in this thesis and describing potential avenues for future research.

# CHAPTER 2

## The CompSOC: Mixed Time-Criticality Platform

Real-time applications require guarantees that they will meet their timing requirements. To be able to do this, the platform on which they execute must be predictable. This is further complicated whenever real-time applications share resources with other non real-time applications. The contention for shared resources must be taken into account when providing guarantees. This is not trivial, especially on mixed-time criticality systems where real-time and non real-time applications can share resources. The behaviour of non real-time applications might not be predictable, and therefore the contention for the resource might be unpredictable too.

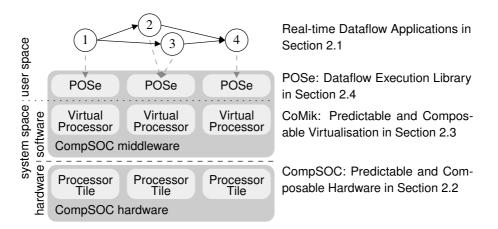

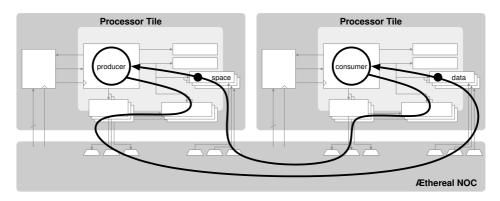

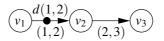

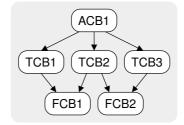

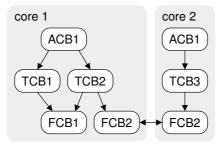

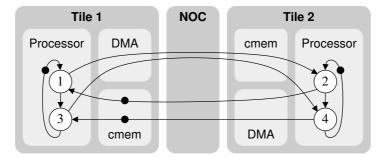

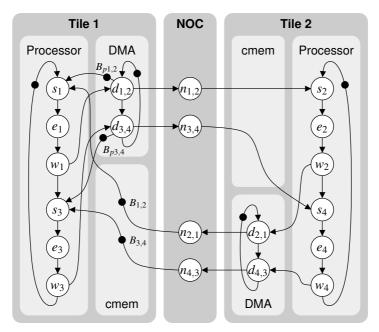

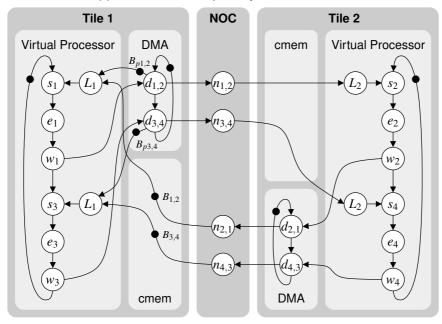

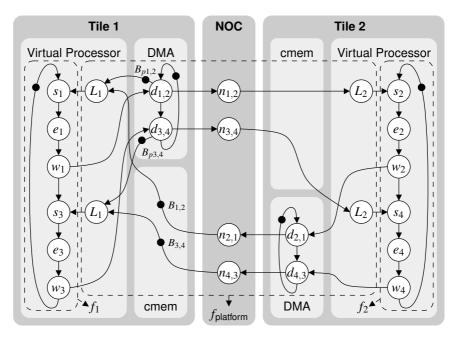

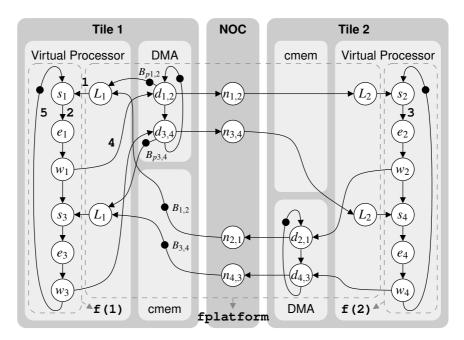

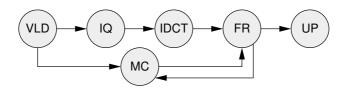

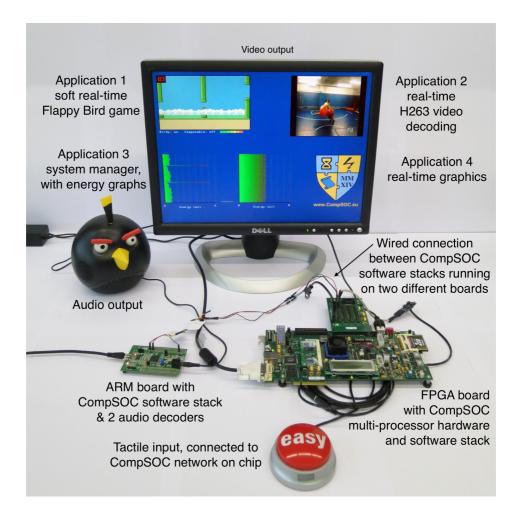

In this chapter, we describe the CompSOC platform that provides a composable and predictable platform for the purpose of running applications of mixed time criticality. This is achieved by CompSOC's hardware and software framework, as illustrated in Figure 2.1. Dataflow applications are executed on the platform using the POSe OS and composably isolated using the CoMik microkernel. The CompSOC hardware platform enables worst-case bounds to be derived for both computation and communication. For real-time applications, a worst-case timing analysis is used to verify that the application meets its timing requirements. In Section 2.1 we explain how dataflow is used to analyse the behaviour of real-time applications.

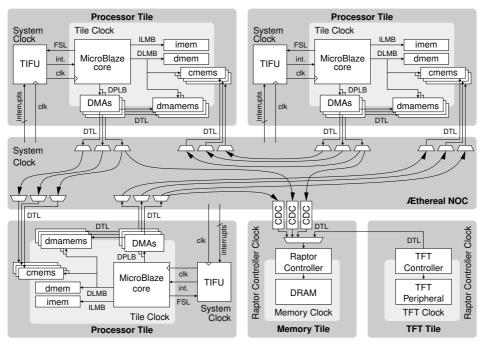

The worst-case timings of the application depends on the hardware resources to which it is mapped. In Section 2.2, we describe the CompSOC hardware platform, an instance of which is illustrated in Figure 2.2a. We explain how the application's mapping to

Figure 2.1: CompSOC high-level overview.

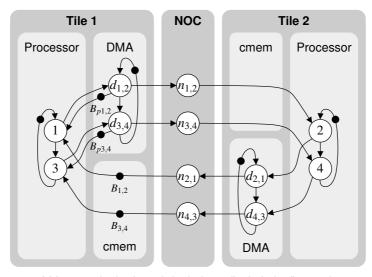

CompSOC's hardware resources affects its timing and how we take this into account in the application's dataflow model. Both the dataflow application's tasks and communication require physical resources and take time to complete. In Section 2.2.3, we explain how a mapped C-HEAP FIFO is modelled as a dataflow graph that when

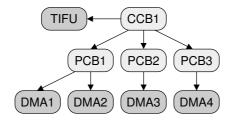

To enable composable and predictable communication between processing cores, we contribute composable memory architectures to the CompSOC processing tile in Section 2.2.1. We describe how the communication and memory architecture of the tile is configured to enable composable inter-tile communication, presenting two composable configurations and explain the trade-offs between them. To support precisely timed virtualisation of DVFS management and interrupts we further contribute the TIFU to the CompSOC processing tile and describe it in detail in Section 2.2.4.

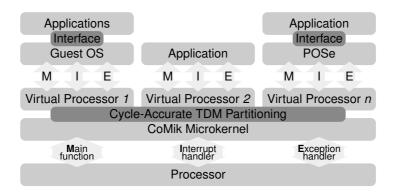

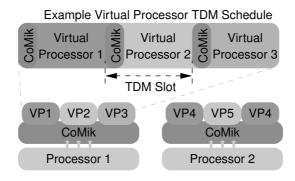

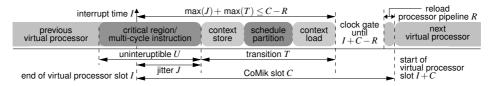

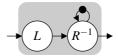

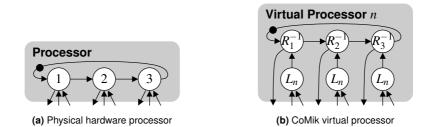

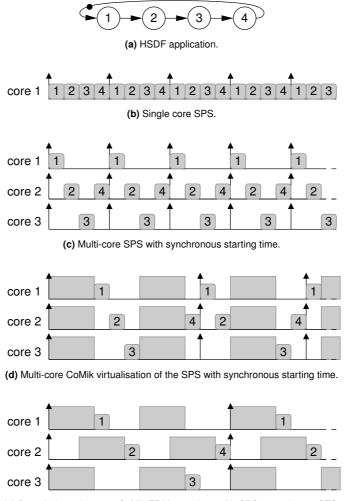

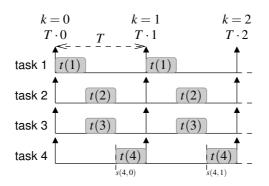

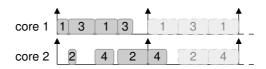

Composable virtualisation provides temporal isolation between applications, enabling mixed time-criticality applications to share physical resources [31, 34]. To achieve this, we contribute the CoMik microkernel in Section 2.3. CoMik divides the processor into multiple composable virtual processors enabling applications of various criticalities to co-exist on the same physical processor without interfering by even a single cycle. This is achieved using TDM scheduling of virtual processors on the physical processor. By modelling the TDM scheduling as a dataflow latency-rate server, the composable virtualisation can be incorporated into the application dataflow graph for temporal analysis.

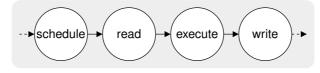

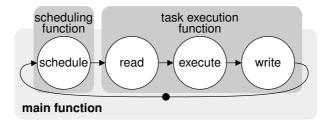

CoMik allows the user a choice of which OS and/or Model of Computation (MOC) to use. It provides an interface similar to the physical processor, taking a pointer to a main function, and interrupt handler and an exception handler, as illustrated in Figure 2.2b. To enable the execution of dataflow applications, we contribute the POSe Real-Time Operating System (RTOS) in Section 2.4. This is achieved by structuring applications following the dataflow paradigm, with tasks as actors that communicate via C-HEAP FIFOs as edges. We further describe how the POSe MOE is modelled as a dataflow graph

(a) CompSOC hardware platform instance.

(b) CompSOC software hierarchy.

Figure 2.2: CompSOC platform overview.

enabling the POSe OS to be incorporated into the application dataflow graph for temporal analysis.

After describing how real-time applications can be modelled and analysed as dataflow graphs (Section 2.1 and Section 2.4, respectively), and presenting the CompSOC platform (Section 2.2) that enables dataflow applications to be executed, in Section 2.5 we contribute an algorithm that takes the dataflow model of a mapped application that is mapped onto the CompSOC platform, and makes a combined application and CompSOC platform dataflow graph.

## 2.1 Real-time Dataflow Applications

Real-time applications have timing requirements that must be met. To provide assurances, the timing of the applications must be analysed. This is commonly achieved by formalising applications using a MOC. Many types of MOC exist, with varying degrees of analysability and expressiveness. The CompSOC platform is able to execute applications using the Kahn Process Network (KPN), Cyclo-Static Dataflow (CSDF), Synchronous Dataflow (SDF) and Homogeneous Synchronous Dataflow (HSDF) MOCs, ranging from most to least expressive. The choice of MOC is a trade-off, as generally the more analysable a MOC is then the less expressive it is also [14]. It is harder to express an application in a more restrictive MOC. As such, the most analysable MOCs are also the most restrictive to program for, adding to design time.

Figure 2.3: Dataflow expressiveness.

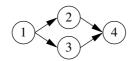

In this thesis, we focus solely on the dataflow MOCs due to their analysability. Figure 2.3 illustrates the hierarchy of expressiveness of the dataflow MOCs. Note that KPN is not a dataflow MOC.

SDF is more expressive than HSDF, and all HSDFGs are Synchronous Dataflow Graphs (SDFGs). Similarly, CSDF is more expressive than SDF, and all SDFGs are Cyclo-Static Dataflow Graphs (CSDFGs). It is shown in [14] that all CSDFGs can be represented as timing-equivalent HSDFGs. This means that applications can be modelled as either of the more expressive SDF or CSDF MOCs while still being temporally analysable using the HSDF formalism. The techniques presented in this thesis can be used on applications that follow the HSDF MOC, and on applications that follow other dataflow MOCs that are translatable to HSDF for temporal analysis, such as SDF and CSDF.

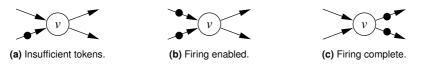

Figure 2.4: HSDF actor firing.

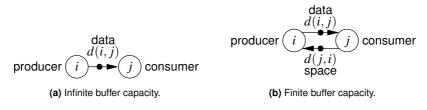

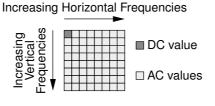

An HSDFG is a graph, with actors represented by the graph vertices and FIFO communication between actors represented by directed edges. Data is communicated along the edges of the graph in atomic tokens, represented as a black circle on the edge. Edges have an infinite token capacity, meaning that the number of tokens on an edge does not inhibit the production of more tokens on that edge. HSDF actors require a single token on each incoming edge before they are able to fire, i.e. the task has the data required for execution. This is illustrated in Figure 2.4 where in Figure 2.4a actor v is unable to fire as one incoming edge has no tokens, whereas actor v is enabled to fire in Figure 2.4b as there is one token on each of its incoming edges. Depending on the scheduling scheme actors can fire (at the earliest) as soon as they are able (Self-Timed Schedule (STS)) or possibly defer firing until a later moment, e.g. when using a Static-Periodic Schedule (SPS). When an actor fires, a token is consumed from each incoming edge. Upon completing execution, one token is produced on each outgoing edge, as illustrated in Figure 2.4c.

#### 2.1.1 Resource Constraints

To execute a dataflow application, it must be mapped onto a suitable platform, such as the CompSOC platform. Whereas the only constraint on actor firing in an HSDFG is sufficient token availability, mapped dataflow applications also have resource constraints in addition to data dependencies. These implementation constraints are due to finite resource capacity, e.g. FIFO buffer capacity. In order to take them into account within the HSDFG framework, they must be modelled as a token dependency. This is achieved by adding additional HSDFG edges and tokens to the original application HSDFG.

#### Mapping

The nature and timing of the resource constraint depends on the resource to which the dataflow component is mapped. Dataflow applications consist of actors that are implemented by computational tasks and edges that are implemented by C-HEAP FIFO buffers. On a multi-processor system, individual tasks are mapped onto a processor. The worst-case execution time of the task depends on the type of processor to which it is mapped and the frequency at which the processor operates. The worst-case work of the task is the worst-case number of cycles that must execute on the processor before the task is complete, and therefore does not depend on the processor's frequency. This makes worst-case work a useful measurement of task execution duration for DVFS management.

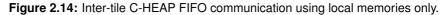

Figure 2.5: A C-HEAP FIFO mapping.

The application's communication must also be mapped to platform resources, as illustrated in Figure 2.5. The dataflow edge that is implemented as a C-HEAP buffer can be mapped in the local scratchpad memory of either the producing or consuming processing tile, or in a larger shared memory that is accessible via the Network on Chip (NoC). When accessing memory locations via the NoC, the communication actions must be mapped onto hardware communication resources, such as DMA modules and NoC connections. As with the computational tasks, the use of these resources costs time. The dataflow MOC does not allow graph edges to be annotated with an execution duration. For analysis, additional actors are therefore added to the edges of an application's dataflow graph, that represent the duration of the operation on the communication resources. This is explained in more detail for C-HEAP communication in Section 2.2.2.

#### Auto-concurrency constraint

An HSDF actor can execute infinitely many times auto-concurrently, with token availability being the only constraint, e.g. the actor illustrated in Figure 2.6a has no incoming edges and may fire infinitely many times auto-concurrently (at the same time in parallel) as it is always enabled to fire. For instance, depending on the scheduler, a task executing on a processor might be prevented from, or have limited auto-concurrency.

Figure 2.6: HSDF actor auto-concurrency.

An auto-concurrency constraint on an actor can be modelled in a HSDFG by adding an additional self-edge to the actor concerned. A self-edge is a directed edge where the

#### 2.1. REAL-TIME DATAFLOW APPLICATIONS

source and destination actor are the same. It is governed by the same rules as other HSDF edges, and therefore in order for the actor to fire, at least one token must be present on the edge before the actor is enabled to fire. As the actor will only produce a token on this edge after it has consumed one from it, auto-concurrency is limited by the number of initial tokens on the edge, e.g. one initial token completely prevents auto-concurrency, while two tokens allows two iterations of the actor to fire concurrently.

The scheduling schemes described in this thesis do not schedule application tasks auto-concurrently. They are therefore modelled by actors with a self-edge containing a single initial token. For simplicity of illustration, in this thesis self-edges are omitted from actors in HSDFGs diagrams, unless required in the diagram to differentiate actors without an auto-concurrency constraint, or it is otherwise stated.

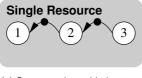

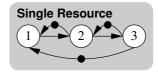

#### Single-Resource Concurrency Constraint

When mapping an HSDF application to an actual Multiprocessor System on Chip (MPSoC) platform, it is not always possible, or desirable, for each actor to be mapped onto its own processor. As such, the application's tasks will have to share the processor that they are mapped onto. Instructions from only one task at a time can be processed on a single threaded processor, so scheduling must be used to arbitrate which task gets to execute and at what time.

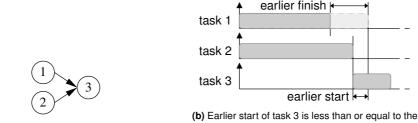

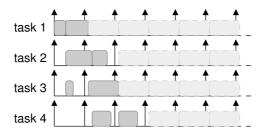

In this thesis, task-level scheduling within an application is assumed to be performed co-operatively. A task that is executing, cannot be pre-empted by another task. As such, only one task belonging to an application can execute per processor at any given time. Under a STS, actors start firing as soon as they have sufficient tokens to do so, but multiple actors on the same processor may concurrently have sufficient tokens to fire, e.g. Figure 2.7a illustrates a single resource on which all three actors are able to fire concurrently. The single-resource constraint is therefore not captured by the STS.

(a) Concurrently enabled actors.

**(b)** Cycle of resource constraint control edges.

Figure 2.7: Single-resource constraint control edges.

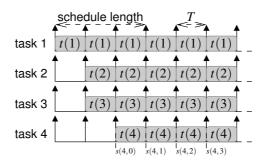

Token availability is the only method to control the firing of HSDF actors that are executing following a STS. The single resource constraint is therefore taken into account using (so called) "control" edges in the HSDFG. For the example illustrated in Figure 2.7a, control edges are added in Figure 2.7b to ensure that only one actor can fire at a time. The control edges form a cycle, with one of the edges containing a single initial token, ensuring that only one actor at a time is able to fire. The actors therefore fire following

a Static-Order Schedule (SOS), starting with the actor that has the initial token on its incoming control edge (actor 1 in the example).

#### **Finite FIFO Capacity**

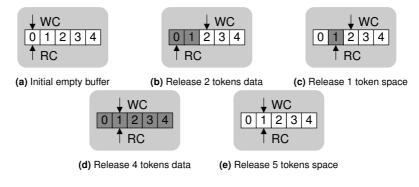

A FIFO buffer that is mapped onto a hardware platform has a finite capacity. The HSDF edges that represent inter-actor FIFOs have an infinite token capacity. A FIFO buffer with finite capacity is modelled using two directed edges. One edge representing the direction of data transfer between the two actors. The other edge represents the direction of transfer of free space in the buffer.

Figure 2.8: HSDFG FIFO buffer capacity representation.

## 2.1.2 HSDFG and Schedule Formalism

We continue by presenting the background material on HSDFG schedule formalism that enables temporal analysis of dataflow applications. In this section, we present schedule admissibility and analysis techniques for STS, Worst-Case Self-Timed Schedule (WCSTS) and SPS schemes. These are applied in Chapter 4 and Chapter 5 to enable conservative DVFS for real-time applications.

The firing time of an actor depends on the availability of tokens on its incoming edges and the scheduling scheme. Under a Self-Timed Schedule (STS), the actors start firing as soon as there are enough tokens to do so. Whereas in a Static-Periodic Schedule (SPS), actors start firing at static periodic intervals that are derived to ensure token availability. CompSOC executes dataflow applications following a STS. The actor firing times in an STS schedule depends on actual actor firing durations. For dataflow applications, these times depend on task execution times that can be data-dependent.

Figure 2.9: HSDFG composed of actors, edges and initial tokens.

A HSDFG G, such as that illustrated in Figure 2.9 is represented using the tuple (V, E, t, d). V is the finite set of annotated vertices. The vertices are dataflow actors. E is