# Better than Worst-Case Design for Streaming Applications under Process Variation

# Better than Worst-Case Design for Streaming Applications under Process Variation

## PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.Ch.A.M. Luyben, voorzitter van het College voor Promoties in het openbaar te verdedigen

op vrijdag 13 december 2013 om 12.30 uur

$\operatorname{door}$

Davit Mirzoyan

Master of Science Kungliga Tekniska Högskolan, Zweden geboren te Yerevan, Armenië Dit proefschrift is goedgekeurd door de promotor:

Prof.dr. K.G.W. Goossens

Copromotor:

Dr. K.B. Åkesson

Samenstelling promotiecommissie:

| Rector Magnificus,           | voorzitter                                    |

|------------------------------|-----------------------------------------------|

| Prof.dr. K.G.W. Goossens,    | Technische Universiteit Delft, promotor       |

| Dr. K.B. Åkesson,            | Technische Universiteit Eindhoven, copromotor |

| Prof.dr. K.L.M. Bertels,     | Technische Universiteit Delft                 |

| Prof.dr. H.J. Sips,          | Technische Universiteit Delft                 |

| prof.dr. J. Pineda de Gyvez, | Technische Universiteit Eindhoven             |

| prof.dr. H. Corporaal,       | Technische Universiteit Eindhoven             |

| Dr. S.D. Cotofana,           | Technische Universiteit Delft                 |

The work in this thesis is supported by the Dutch government in their STW research program within the NEST project 10346.

#### Copyright 2013 Davit Mirzoyan

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means without the prior written permission from the copyright owner.

Printing by Ipskamp Drukkers.

Dedicated to my family for their unfailing encouragement and support

### ACKNOWLEDGMENTS

I am glad to have this opportunity to express my gratitude to all who directly or indirectly had their contribution in this work. I would like to thank Prof. Koen Bertels at Delft University of Technology for all the practical support during these four years. I extend my gratitude to Ms. Lidwina Tromp, the secretary at the Computer Engineering laboratory, who has always been very helpful with practical matters. I acknowledge fellow Ph.D. students Andrew Nelson, Ashkan Beyranvand Nejad, a former postdoctoral researcher Dr. Anca Molnos, and all the staff at the Computer Engineering laboratory. Being affiliated with Delft University of Technology, my workplace was arranged at Eindhoven University of Technology, where I have always worked. Over the course of these years, I have been fortunate to work in such a friendly environment, as in the Electronic Systems group. My deep appreciation to the group for all the hospitality that I have been shown.

$\sim$

I am sincerely grateful that four years ago Prof. Kees Goossens gave me the opportunity to work with him. I have been fortunate to have a mentor with such a strong work ethic. My deepest gratitude to Dr. Benny Åkesson, my co-supervisor and once a student of Prof. Goossens. Working with him has been a real pleasure. I have had the opportunity to enjoy beautiful Porto, Portugal with Benny on a business travel, which turned out to be very memorable, as we can agree. I would like to acknowledge Dr. Sander Stuijk, who always found time to give me insight into the theory of data flow graphs. Discussions with him have always been fruitful. I extend my gratitude to Prof. José Pineda de Gyvez for the circuit-level discussions that he has provided on multiple occasions. They were always helpful. My special appreciation goes to Ms. Marja de Mol - Regels and Ms. Rian van Gaalen, the truly kind secretaries at the Electronic Systems group. I would like to thank Rian for organizing the "uurtje Nederlands", an hour of weekly delightful dutch lessons, for us and for all the enthusiasm she has shown on different occasions.

I have always enjoyed the working environment in our office, with great office mates Firew Siyoum, Manil Dev Gomony, Cedric Nugteren, Roel Jordans and Luc Vosters. During these four years, we have had all the interesting discussions covering a variety of topics, such as science, technology, work, etc. I would like to add that I feel fortunate to have known Firew Siyoum, Manil Dev Gomony and Karthik Chandrasekar during these years. Last but not the least, I extend my gratitude to all the staff members at the Electronic Systems group, who have made these years more enjoyable.

From the bottom of my heart, I would like to thank my family, my mother Juletta Makaryan, my father Razmik Mirzoyan, and my lovely sister Yevgeniya Harutyunyan, for all the support and encouragement over the course of these years.

I cannot finish writing these acknowledgments without expressing my deepest gratitude and admiration towards my heavenly Father, the Lord Jesus Christ, for his unconditional love and boundless riches for those who love him; his mercies are new every morning. I thank him for the increasing amount of strength he has given me; as it is written "Even youths grow tired and weary, and young men stumble and fall; but those who hope in the Lord will renew their strength. They will soar on wings like eagles; they will run and not grow weary, they will walk and not be faint." Isaiah 40:30-31.

### SUMMARY

Modern multimedia and wireless applications require considerable computational power due to an increasing amount of functionality added to these applications. Additionally, many portable consumer electronics impose requirements on low power consumption for long battery life. To meet these requirement, streaming applications are implemented on a multi-processor system-on-chip (MPSoC), where multiple (slower) processing cores exploit task and data-level parallelism to increase performance. The hardware components inside an MPSoC are usually connected to each other by a scalable network on chip (NoC). To be able to analyze the timing of an application implemented on an MPSoC and provide timing guarantees at design time, all MPSoC components must be predictable. To remove the bottleneck of global clock-tree routing and reduce a major source of power consumption, multi-processor systems are implemented with the globally asynchronous, locally synchronous (GALS) design style. GALS architectures enable the use of voltage-frequency islands to additionally reduce power consumption by scaling the frequency (voltage) of individual components in an MPSoC.

$\mathbf{O}$

To reduce circuit area and thus integrate more functionality on a chip die, CMOS technology has traditionally been scaled down. However, scaling in the nanoscale era has brought significant variability in the manufacturing process. This variability or inability to precisely control the manufacturing process results in significant variation in the maximum supported frequency of hardware components in a multi-processor system. Given this variation, it becomes difficult to provide timing guarantees for an application mapped to a multi-processor system. As a solution, circuits are conventionally implemented with design margins or guard-bands to guarantee the target frequency of hardware components inside an MPSoC. Under this design paradigm, known as worst-case design, an application sees the hardware components in a multi-processor platform with deterministic minimum frequencies, leading to a mapping of the application tasks to the hardware components, such that a certain timing requirement (e.g. throughput or latency) imposed on the application is satisfied. However, worst-case design results in a considerable up-sizing of circuit area and in increased power consumption. Because of this, the benefits of technology scaling can be lost with worst-case design.

This thesis deals with the design of real-time streaming applications constrained by a throughput requirement with reduced design margins, referred to as better than worst-case design. With better than worst-case design, the area, the power consumption and the leakage of a circuit are reduced. Smaller circuit area and thus die size results in a larger number of gross dies on a wafer. However, the target maximum supported frequency of hardware components in a multi-processor system is not guaranteed anymore, and the spread in the maximum supported frequency of hardware components needs to be considered when mapping an application to the platform. The goal of this thesis is to maximize the number of good dies that satisfy the throughput requirement of a real-time streaming application.

To this end, a design flow consisting of three stages is presented in this thesis. In the first stage of the flow, a streaming application is allocated to a NoC-based multiprocessor system with voltage-frequency islands, where each hardware component is characterized by process-induced frequency variations. The goal is to maximize the timing yield, which is a system-level metric quantifying the percentage of manufactured chips that satisfy the timing requirement of the application. Maximizing the timing yield is essential as the number of good dies is given by the product of the number of gross dies and timing yield. Two mapping approaches are possible: single and multiple bindings for manufactured chips. Multiple bindings can exploit the availability of within-die variation-induced faster and slower processing cores on the same chip by adopting the allocation of application tasks. Following the mapping stage, trade-offs between the number of voltage-frequency islands, as well as the number of clock-frequency levels provided to each island, (area and power consumption cost) and timing yield are performed. Having decided on the binding (or a set of bindings), a set of voltage-frequency island configurations and a number of clock-frequency levels per island, the number of good dies on a wafer is evaluated for different guard-band reduction values in the third and final stage of the flow. The reduction in guard-bands providing the most good dies is selected. We show on both synthetic and real applications that the proposed design flow can increase the number of good dies by up to 9.6% and 18.8% for designs with and without fixed SRAM and IO blocks, respectively.

## SAMENVATTING

Moderne multimedia en draadloze applicaties vereisen aanzienlijke rekenkracht als gevolg van hun toenemende functionaliteit. Bovendien eist veel draagbare consumentenelektronica een laag stroomverbruik om een lange levensduur van de batterij te garanderen. Om aan deze eisen te voldoen worden streamingapplicaties geïmplementeerd op een multi-processor system-on-chip (MPSoC), waarbij meerdere (tragere) processorkernen taak en data-parallellisme benutten om de prestaties te verhogen. De hardwarecomponenten in een MPSoC zijn meestal met elkaar verbonden door middel van een schaalbaar network-on-chip (NoC). Alle MPSoC onderdelen moeten voorspelbaar zijn om tijdsanalyse van applicaties te kunnen geven en om tijdsgaranties te kunnen geven tijdens de ontwerpfase. Deze systemen worden ontworpen volgens het globally asynchronous, locally synchronous (GALS) principe om zo de bottleneck van een globale klokfrequentieboom te omzeilen en om een belangrijke bron van vermogen te verlagen. GALS architecturen maken het mogelijk om frequentie-spanningseilanden te vormen die het vermogensgebruik verder verminderen door de frequentie (of spanning) van componenten in een MPSoC individueel te schalen.

Het schalen van CMOS technologie heeft er voor gezorgd dat chip oppervlakte verkleind werd om zodoende meer functionaliteit op een enkele chip te kunnen integreren. Echter, het schalen naar nanometer-technologie heeft aanzienlijke veranderlijkheid gebracht in het fabricageproces. Deze veranderlijkheid (het onvermogen om het productieproces te controleren) resulteert in aanzienlijke variaties in de maximaal ondersteunde frequentie van componenten in een multi-processor systeem. Door deze variaties wordt het moeilijk om tijdsgaranties te geven voor applicaties die afgebeeld zijn op zulke systemen. Als oplossing worden chips gebruikelijk uitgerust met marges (zogenoemde guard-bands) om vooraf vastgestelde frequenties toch te kunnen garanderen. Volgens deze ontwerpstijl (worst-case ontwerp) ziet een applicatie dat alle componenten van een multi-processor platform deterministische frequenties hebben. Dit leidt er toe dat een afbeelding van applicatietaken op de hardwarecomponenten aan vooraf bepaalde tijdsvereisten kan voldoen (bijvoorbeeld doorvoersnelheid of latentie). Echter, de worst-case ontwerpstijl resulteert in aanzienlijk grotere chips en in een verhoogd stroomverbruik. Hierdoor kunnen de voordelen van het schalen van CMOS weer verloren gaan.

Dit proefschrift behandelt het ontwerpen van real-time streaming-applicaties die beperkt zijn door een doorvoersnelheidseis met verkleinde marges, bekend als de beter dan worst-case ontwerpstijl. Een dusdanig ontwerp verlaagt het oppervlaktegebruik en vermindert het stroomverbruik en de lekstromen. Een kleiner oppervlaktegebruik resulteert in een groter aantal chips per wafer. Echter worden de vooraf vastgestelde frequenties niet meer gegarandeerd en moet de spreiding van de maximaal ondersteunde frequentie in overweging genomen worden wanneer een applicatie wordt afgebeeld op een platform. Het doel van dit proefschrift is om het aantal goede chips dat aan de doorvoersnelheidseis van een real-time streaming-applicatie voldoet te maximaliseren.

Hiertoe wordt een ontwerp dat bestaat uit drie fases gepresenteerd. In de eerste fase wordt een streaming-applicatie toegewezen aan een NoC-gebaseerd multi-processor systeem met frequentie-spanningseilanden, waarbij elke hardwarecomponent gekarakteriseerd wordt door proces-gestuurde frequentievariaties. Het doel is om de yield te maximaliseren: een systeemniveau metriek die kwantificeert welk percentage van de geproduceerde chips aan de tijdsvereiste van de applicatie voldoen. Het maximaliseren van de yield is essentieel, omdat het aantal goede chips wordt bepaald door het product te nemen van het bruto aantal chips en de yield. Twee afbeeldingstechnieken zijn mogelijk: ofwel een enkele afbeelding ofwel meerdere afbeeldingen. Meerdere afbeeldingen maken de toekenning van applicatietaken adaptief. Hierdoor kan rekening gehouden worden met de aanwezigheid van variaties in snelheden van processorkernen binnen een chip. Volgend op de toekenningsfase worden de vield en de compromissen (oppervlaktegebruik versus vermogensgebruik) van het aantal frequentie-spanningseilanden en frequentieniveaus bepaald. In de derde en laatste fase van het ontwerp wordt het aantal goede chips geëvalueerd voor verschillende guard-band reducties. Uiteindelijk wordt een guard-band gekozen die het grootste aantal goede chips oplevert. We tonen aan dat de gepresenteerde ontwerptechniek voor zowel synthetische als echte applicaties het aantal goede chips kan verhogen met 9.6% of 18.8%, waarbij het eerste resultaat er vanuit gaat dat er vaste SRAM en IO-blokken zijn die niet meeschalen met guard-band reducties.

# Content

| 1        | Intr | oduction 1                         |

|----------|------|------------------------------------|

|          | 1.1  | Real-time embedded systems 1       |

|          | 1.2  | Manufacturing process variation    |

|          | 1.3  | Problem statement                  |

|          | 1.4  | Overview of solution               |

|          | 1.5  | Contributions                      |

| <b>2</b> | For  | nal Modeling 11                    |

|          | 2.1  | Platform graph                     |

|          | 2.2  | Variation in hardware resources    |

|          |      | 2.2.1 Global variation             |

|          |      | 2.2.2 Local variation              |

|          | 2.3  | Clock-frequency characterization   |

|          | 2.4  | Resource-aware application graph   |

|          | 2.5  | Bound application graph            |

|          |      | 2.5.1 Modeling resource allocation |

|          |      | 2.5.2 Throughput computation       |

|          |      | 2.5.3 Scheduling                   |

|          | 2.6  | Summary                            |

| 3        | Var  | iation-aware mapping 33            |

|          | 3.1  | Optimization problems              |

|          | 3.2  | Single-binding                     |

|          |      | 3.2.1 Best-effort applications     |

|          |      | 3.2.2 Firm real-time applications  |

|          |      | 3.2.3 Soft real-time applications  |

0

~

|   | 3.3             | Multiple-bindings                                                                                              | 39  |

|---|-----------------|----------------------------------------------------------------------------------------------------------------|-----|

|   | 3.4             | Implementation algorithms                                                                                      | 40  |

|   |                 | 3.4.1 Exhaustive algorithm                                                                                     | 40  |

|   |                 | 3.4.2 Heuristic algorithm                                                                                      | 42  |

|   | 3.5             | Experimental results                                                                                           | 46  |

|   |                 | 3.5.1 Experimental setup                                                                                       | 47  |

|   |                 | 3.5.2 Evaluation results $\ldots \ldots \ldots$ | 49  |

|   | 3.6             | Summary                                                                                                        | 59  |

| 4 | Volt            | tage-frequency island partitioning                                                                             | 63  |

|   | 4.1             | Outline of CGU architectures                                                                                   | 64  |

|   | 4.2             | Heuristic Partitioning Algorithms                                                                              | 65  |

|   |                 | 4.2.1 Single binding                                                                                           | 66  |

|   |                 | 4.2.2 Multiple bindings                                                                                        | 69  |

|   | 4.3             | Experimental results                                                                                           | 71  |

|   |                 | 4.3.1 Experimental setup                                                                                       | 71  |

|   |                 | 4.3.2 Evaluation results                                                                                       | 73  |

|   | 4.4             | Summary                                                                                                        | 86  |

| 5 | Bet             | ter than worst-case design                                                                                     | 89  |

|   | 5.1             | Number of good dies                                                                                            | 89  |

|   | 5.2             | Variation characterization                                                                                     |     |

|   | 5.3             | Experimental setup                                                                                             | 92  |

|   |                 | 5.3.1 Evaluation results                                                                                       |     |

|   | 5.4             | Summary                                                                                                        | 99  |

| 6 | Rel             | ated work                                                                                                      | 101 |

| Ŭ | 6.1             | Mitigating variation at the circuit level                                                                      |     |

|   | 6.2             | Task allocation for MPSoC                                                                                      |     |

|   | 6.3             | VFI partitioning                                                                                               |     |

|   | 6.4             | Variation-aware throughput analysis                                                                            |     |

| 7 | Cor             | clusions and future work                                                                                       | 105 |

| • | 7.1             | Conclusions                                                                                                    |     |

|   | 7.2             | Future directions                                                                                              |     |

| Δ | Glo             | ssary                                                                                                          | 119 |

|   | A.1             | List of abbreviations                                                                                          |     |

|   | A.2             | List of symbols                                                                                                |     |

| в | Apr             | olication SDF graphs                                                                                           | 123 |

|   |                 |                                                                                                                |     |

| С | Abo             | but the author                                                                                                 | 129 |

| D | $\mathbf{List}$ | of publications                                                                                                | 131 |

# LIST OF FIGURES

| 1.1 | Process-induced spread in frequency of a hardware component for<br>worst-case and better than worst-case designs, where $f_{tq}$ is the |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|----|

|     | target frequency.                                                                                                                       | 4  |

| 1.2 | Circuit area and clock period trade-off curves for slow, nominal and fast process corners. The timing margin accounting for within-die  |    |

|     | process variation is shown by an arrow.                                                                                                 | 4  |

| 1.3 | An application (1:) constrained by a throughput requirement is<br>allocated to a multi-processor platform (2:) under worst-case and     |    |

|     | better than worst-case designs.                                                                                                         | 6  |

| 1.4 | Design flow                                                                                                                             | 7  |

| 2.1 | The template of a multi-processor platform consisting of processing                                                                     |    |

|     | elements connected to each other by an interconnect. The process-                                                                       |    |

|     | ing elements and the interconnect are placed in different voltage-                                                                      |    |

|     | frequency islands. The separation between clock domains is shown                                                                        |    |

|     | by the dotted lines                                                                                                                     | 13 |

| 2.2 | $f_q^r$ PDF (due to global variation) for a processing element with                                                                     |    |

|     | $\mu_q^r = 300$ MHz, $\sigma_q^r = 12$ MHz; $f_l^r$ PDFs (due to local variation)                                                       |    |

|     | with respect to $f_q^r = 273$ , 285 and 297 MHz, $\delta^r = 15$ MHz, $\sigma_l^r = 10$                                                 |    |

|     | MHz; combined PDF of $f^r$ is the convolution of PDFs of $f^r_q$ and $f^r_l$ .                                                          | 16 |

| 2.3 | An example showing how equidistant clock-frequency levels are se-                                                                       |    |

|     | lected for a voltage-frequency island comprising two hardware re-                                                                       |    |

|     | sources                                                                                                                                 | 18 |

| 2.4 | An example illustration of how the probability that an island is                                                                        |    |

|     | operated at a particular clock frequency is computed                                                                                    | 20 |

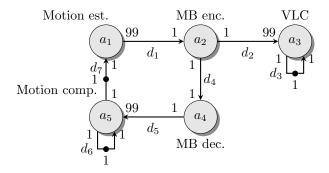

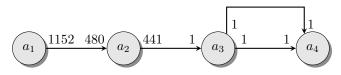

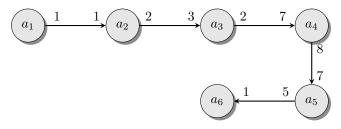

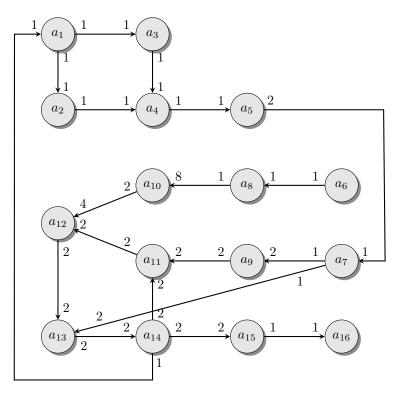

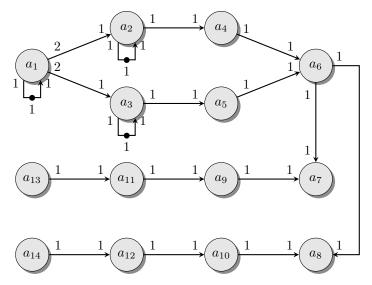

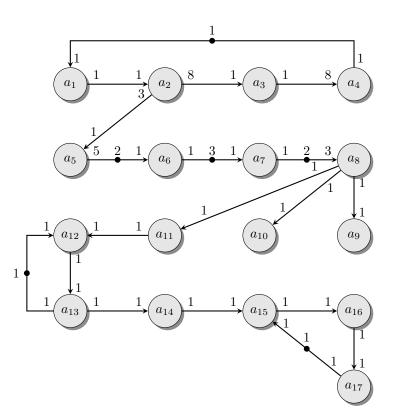

| 2.5 | An example SDF model of an H.263 encoder                                                                                                | 22 |

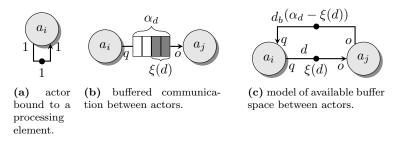

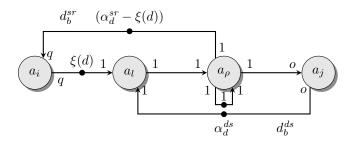

| 2.6  | Modeling resource allocation in an SDF graph                                                                                                                                                                                                         | 27 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.7  | SDF model of a connection in the interconnect.                                                                                                                                                                                                       | 28 |

| 2.8  | Continuous slot reservation strategy in a TDM slot table                                                                                                                                                                                             | 28 |

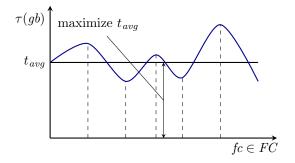

| 3.1  | Throughput against chip-frequency vector for a fixed binding. The average throughput over all chip-frequency vectors is shown by the dotted line.                                                                                                    | 35 |

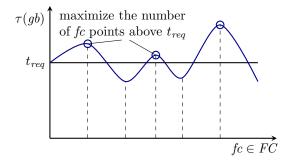

| 3.2  | Throughput against chip-frequency vector for a fixed binding. The timing yield is given by the percentage of $fc$ points (with associated probabilities $pc(gp, fc)$ ) above $t_{req}$ .                                                             | 36 |

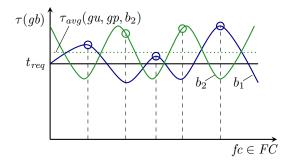

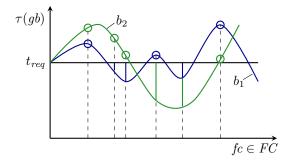

| 3.3  | Throughput against chip-frequency vector for a fixed binding. Two<br>bindings $b_1$ and $b_2$ are shown, where $b_2$ has a higher average through-<br>put but a lower timing yield than $b_1$ .                                                      | 37 |

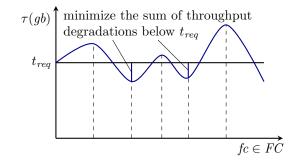

| 3.4  | Throughput against chip-frequency vector for a fixed binding. Se-<br>lecting a binding with the lowest objective function $\zeta$ is equivalent<br>to minimizing the shaded area below $t_{req}$ .                                                   | 38 |

| 3.5  | Throughput against chip-frequency vector for a fixed binding. Two<br>bindings $b_1$ and $b_2$ are shown, where $b_2$ has higher timing yield, but<br>also a higher average throughput degradation, than $b_1$                                        | 39 |

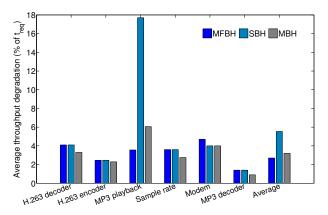

| 3.6  | The multi-processor platform used in the experiments. It consists<br>of three processing elements connected to each other by an inter-<br>connect. The processing elements and the interconnect are placed<br>in separate voltage-frequency islands. | 48 |

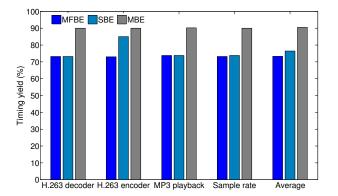

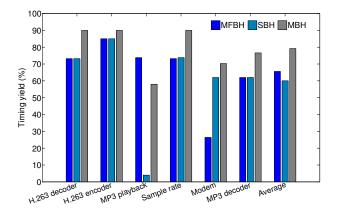

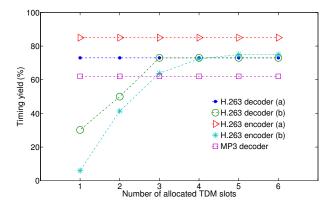

| 3.7  | Timing yield of applications using the exhaustive MFBE, SBE and MBE mapping algorithms for the class of firm real-time applications.                                                                                                                 | 50 |

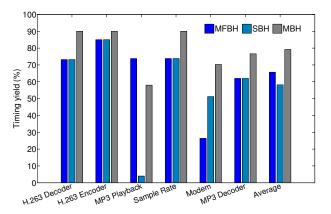

| 3.8  | Timing yield of applications using the heuristic MFBH, SBH and MBH mapping algorithms for the class of firm real-time applications.                                                                                                                  | 52 |

| 3.9  | Timing yield against the number of allocated TDM slots for each dependency edge mapped to a connection in the interconnect for the H.263 decoder, H.263 encoder and MP3 decoder applications.                                                        | 55 |

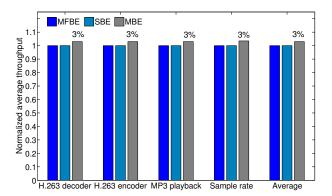

| 3.10 | Normalized average throughput of applications using the exhaus-<br>tive MFBE, SBE and MBE mapping algorithms for the class of<br>best-effort applications.                                                                                           | 56 |

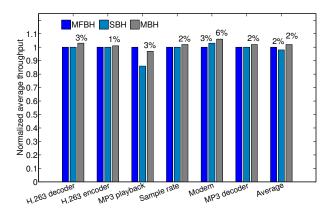

| 3.11 | Normalized average throughput of applications using the heuristic MFBH, SBH and MBH mapping algorithms for the class of best-<br>effort applications.                                                                                                | 50 |

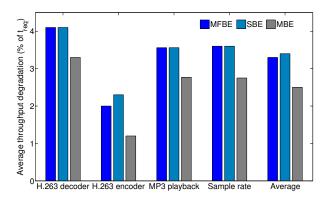

| 3.12 | Average throughput degradation of applications using the MFBE,<br>SBE and MBE heuristic mapping algorithms for the class of soft<br>real-time applications.                                                                                          | 58 |

| 3.13 | Timing yield of applications using the MFBE, SBE and MBE heuristic mapping algorithms for the class of soft real-time appli-                                                                                                                         |    |

|      | cations.                                                                                                                                                                                                                                             | 58 |

| 3.14 | Average throughput degradation of applications using the MFBE,<br>SBE and MBE heuristic mapping algorithms for the class of soft<br>real-time applications.                                                                                                                                                                      | 59 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | Example platform graph comprising three voltage-frequency is-<br>lands. Depending on the clock frequencies of islands, one or an-<br>other binding of the three actors belonging to a resource-aware<br>application graph to the processing elements, which are placed in<br>the islands, is required to achieve high throughput | 71 |

| 4.2  | The multi-processor platform used for the synthetic application. It consists of seven processing elements connected to each other by an interconnect. The processing elements and the interconnect are placed in separate voltage-frequency islands                                                                              | 73 |

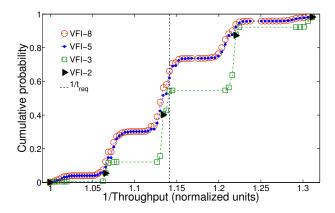

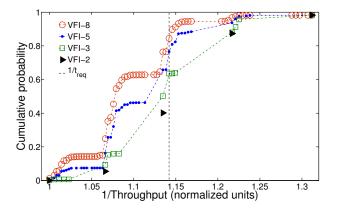

| 4.3  | Throughput CDF for VFI-8, VFI-5, VFI-3 and VFI-2 architectures<br>for the synthetic application. The results presume a single binding<br>of the application to a NoC-based multi-processor platform con-<br>sisting of seven processing elements.                                                                                | 74 |

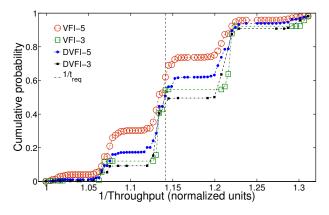

| 4.4  | Throughput CDF for five and three VFI architectures, based on both variation-aware (VFI-4, VFI-2) and deterministic partitions (DVFI-4, DVFI-2).                                                                                                                                                                                 | 76 |

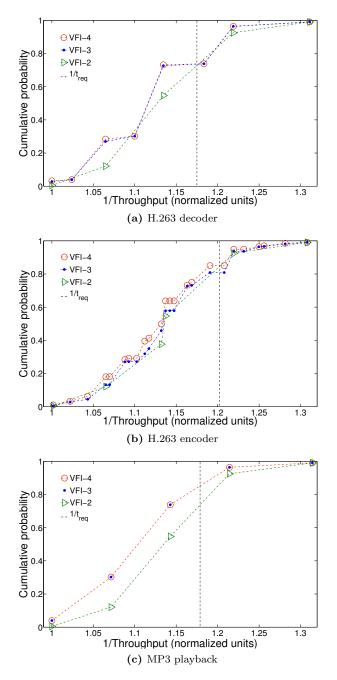

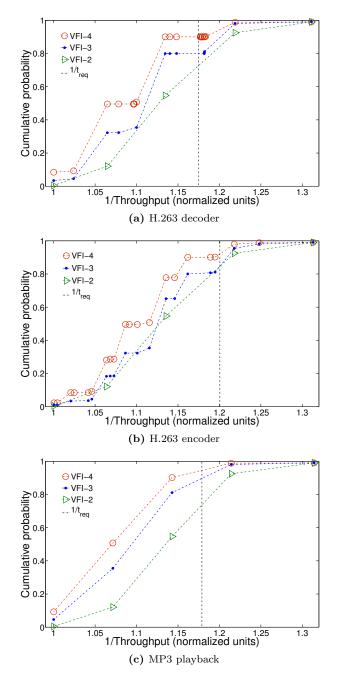

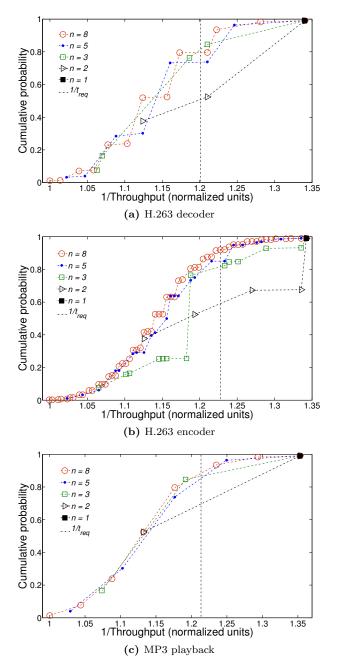

| 4.5  | Throughput CDF for VFI-4, VFI-3 and VFI-2 architectures for the H.263 decoder, H.263 encoder and MP3 playback applications. The results presume a single binding of the application to a NoC-based multi-processor platform consisting of three processing elements.                                                             | 77 |

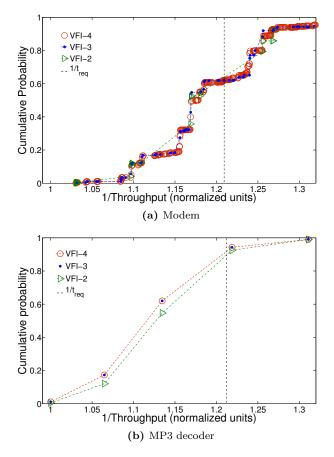

| 4.6  | Throughput CDF for VFI-4, VFI-3 and VFI-2 architectures for<br>the Modem and MP3 decoder applications. The results presume<br>a single binding of the application to a NoC-based multi-processor<br>platform consisting of three processing elements                                                                             | 78 |

| 4.7  | Throughput CDF for VFI-8, VFI-5, VFI-3 and VFI-2 architec-<br>tures for the synthetic application. The results presume multiple<br>bindings (eight) of the application to a NoC-based multi-processor<br>platform consisting of seven processing elements                                                                        | 80 |

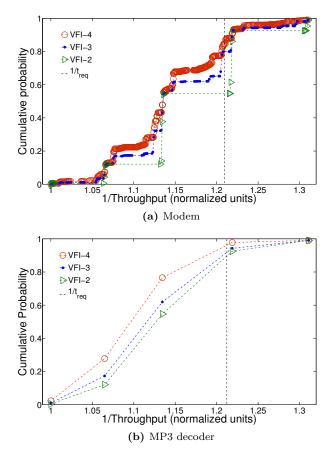

| 4.8  | Throughput CDF for VFI-4, VFI-3 and VFI-2 architectures for the H.263 decoder, H.263 encoder and MP3 playback applications. The results presume multiple binding of the application to a NoC-based multi-processor platform consisting of three processing elements.                                                             | 82 |

| 4.9  | Throughput CDF for VFI-4, VFI-3 and VFI-2 architectures for<br>the Modem and MP3 decoder applications. The results presume<br>multiple binding of the application to a NoC-based multi-processor<br>platform consisting of three processing elements                                                                             | 83 |

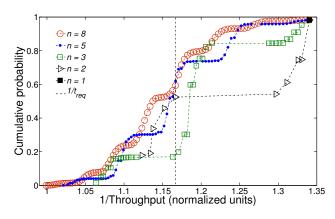

| 4.10       | Throughput CDF for a VFI-5 architecture for the synthetic appli-<br>cation. The results presume a single binding of the application to a<br>NoC-based multi-processor platform consisting of seven processing<br>elements. The graphs are presented for eight, five, three, two and a<br>single clock-frequency levels provided to voltage-frequency islands<br>in the platform graph | 84         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| ۲ 1        |                                                                                                                                                                                                                                                                                                                                                                                       |            |

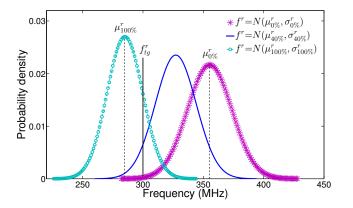

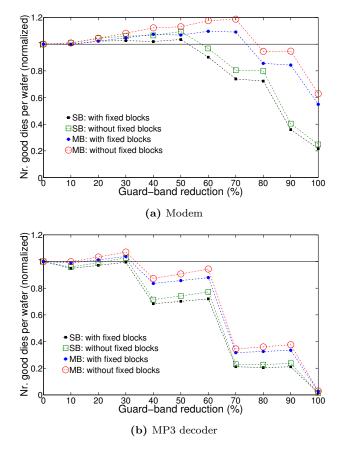

| 5.1<br>5.2 | Combined $f^r$ PDF of a hardware resource due to a 0%, 40%, 100% guard-band reduction. The target frequency $f_{tg}^r$ is 300 MHz, $\sigma_g^r = 4\%$ , $\sigma_l^r = 3.3\%$ , and thus $\sigma_{u\%}^r \approx 5.186\%$ of mean frequency Number of good dies per wafer against reduced guard-band for the synthetic application and a VFI-8 architecture. The graphs are            | 91         |

|            | given for both a single and multiple bindings. Designs with and                                                                                                                                                                                                                                                                                                                       |            |

| 5.3        | without fixed blocks are considered                                                                                                                                                                                                                                                                                                                                                   | 95         |

| 5.4        | synthetic application a VFI-5 architecture. The graphs are given<br>for both a single and multiple bindings. Only a design with fixed<br>blocks is considered                                                                                                                                                                                                                         | 95         |

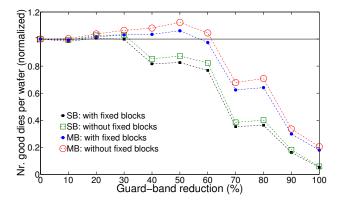

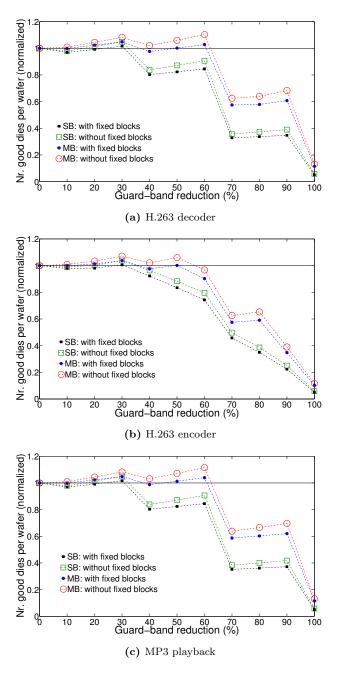

| 5.5        | and a VFI-4 architecture. The graphs are given for both a single<br>and multiple bindings. Designs with and without fixed blocks are<br>considered                                                                                                                                                                                                                                    | 97         |

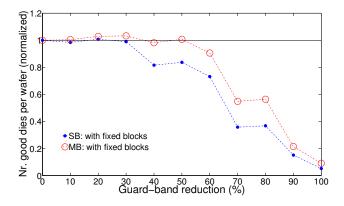

|            | signs with and without fixed blocks are considered                                                                                                                                                                                                                                                                                                                                    | 98         |

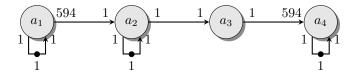

| B.1        | An SDF model of an H.263 decoder.                                                                                                                                                                                                                                                                                                                                                     | 123        |

| B.2        | An SDF model of an H.263 encoder.                                                                                                                                                                                                                                                                                                                                                     |            |

| B.3        | An SDF model of an MP3 playback.                                                                                                                                                                                                                                                                                                                                                      |            |

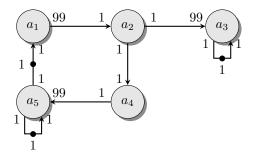

| B.4        | An SDF model of a Sample rate converter.                                                                                                                                                                                                                                                                                                                                              |            |

| B.5<br>B.6 | An SDF model of a Modem                                                                                                                                                                                                                                                                                                                                                               |            |

| в.о<br>В.7 | An SDF model of an MP3 decoder                                                                                                                                                                                                                                                                                                                                                        | 127<br>128 |

| D.1        | mi oprimoutor a symmetre application.                                                                                                                                                                                                                                                                                                                                                 | 140        |

# LIST OF TABLES

| Optimization criteria for application classes                       | 34                        |

|---------------------------------------------------------------------|---------------------------|

| Application SDFG overview.                                          | 47                        |

| Parameters assumed for connection bandwidth, TDM slot-table         |                           |

| size and flit size for the interconnect.                            | 48                        |

| Parameters assumed for random variables modeling the maximum        |                           |

| supported frequency of hardware resources                           | 49                        |

| The run time of exhaustive MFBE, SBE and MBE mapping algo-          |                           |

| rithms                                                              | 51                        |

| The run time of heuristic MFBH, SBH and MBH mapping algorithms.     | 53                        |

| The number of bindings selected by MBH                              | 54                        |

|                                                                     |                           |

|                                                                     |                           |

|                                                                     | 71                        |

|                                                                     | 71                        |

| ·                                                                   | 72                        |

|                                                                     |                           |

|                                                                     |                           |

|                                                                     | 75                        |

|                                                                     | 15                        |

| 1 0 1 0                                                             |                           |

|                                                                     | 80                        |

|                                                                     | 00                        |

| Target frequency and variation-related parameters assumed for hard- |                           |

| ware resources.                                                     | 93                        |

| Timing yield for $u\%$ reduced guard-bands                          | 96                        |

|                                                                     | Application SDFG overview |

$\Rightarrow$

| A.1 | List of symbols                                                      | 120 |

|-----|----------------------------------------------------------------------|-----|

| B.1 | The execution time (in cycles) of actors and the size of data tokens |     |

|     | (in bytes) sent across the dependence edges for the H.263 decoder.   | 124 |

| B.2 | The execution time (in cycles) of actors and the size of data tokens |     |

|     | (in bytes) sent across the dependence edges for the H.263 encoder.   | 124 |

| B.3 | The execution time (in cycles) of actors and the size of data tokens |     |

|     | (in bytes) sent across the dependence edges for the MP3 decoder      | 126 |

| B.4 | The execution time (in cycles) of actors and the size of data to-    |     |

|     | kens (in bytes) sent across the dependence edges for the synthetic   |     |

|     | application.                                                         | 127 |

1

## INTRODUCTION

### 1.1 Real-time embedded systems

Embedded systems contribute to most aspects of our daily activities. They surround us and provide us with entertainment, daily information and assist us in completing our every day tasks. Examples of embedded systems are mobile phones, digital cameras, TV sets, global positioning systems, air traffic management, etc. An important portion of embedded systems is represented by embedded multimedia and wireless systems. Applications in these systems work on streams of audio and video data, and are termed streaming applications. Examples of streaming applications are video decoding (encoding) [63,82] from the multimedia domain and software defined radio [59] from the wireless domain. Streaming applications are usually constrained by a throughput requirement associated with user perception. An example throughput requirement for video decoding is the number of frames per second. Timing requirements exist in firm and soft realtime application classes. In firm real-time applications, such as software-defined radio, violations of the timing requirement are not allowed. Soft real-time applications, such as such as video decoding, are characterized by less stringent timing requirements. In such applications missing a deadline causes only a performance degradation, often evaluated through some quality-of-service parameter. There are also *best-effort applications*, which do not have any timing requirements. An example best-effort application is a graphical user interface. Although there are no timing requirements set on the applications of this class, high performance is preferred by the user.

To enhance user experience, an increasing amount of data must be processed (e.g. to achieve higher video resolutions) and more computationally intensive coding schemes must be implemented. As a result, an increasing computational capability to implement such applications is required. Additionally, many portable consumer electronics, such as mobile phones, digital cameras, and tablets, impose requirements on power consumption for longer battery life. To meet the increasing demand on computational capability and low power consumption, such applications are implemented on a multi-processor system-on-chip (MPSoC) [35, 49, 87, 95], where multiple (slower) processing cores exploit task and data-level parallelism to increase performance without increasing power consumption.

The components inside a multi-processor system were traditionally connected to each other by a bus. However, traditional buses do not provide scalable interconnection. For this reason, a paradigm shift towards network on chips (NoC) based interconnection inside multi-processor systems has been seen in recent years [17]. All hardware components in an MPSoC must be *predictable*, such that the timing of an application implemented on the MPSoC can be formally analyzed and timing guarantees can be given at design time. Present-day MPSoCs are implemented by means of the globally asynchronous, locally synchronous (GALS) design style [48, 60], which was introduced to alleviate the bottleneck of global clock distribution and reduce the related major source of power consumption in multi-processor systems. The GALS architecture is composed of synchronous blocks, communicating with each other on an asynchronous basis. The concept of voltage-frequency islands (VFI), within the GALS design paradigm, enables scaling the frequency (voltage) of each individual hardware component (clusters of components) in a multi-processor system to further reduce power consumption.

Due to rapid technology changes, consumers replace old products with new ones much more frequently. For example, two major products are released annually by mobile phone manufacturers, such as Apple and Samsung. These products offer more and more functionality, leading to a considerable increase in design effort. This imposes requirements on short time to market of products. To address this issue, a *platform-based design* methodology has been proposed [4, 69]. A platform consists of multiple hardware and software components specific to a particular application domain. The software components are application software, middleware and operating systems used for programming the hardware components. A platform, as a result of integration of different components, serves as a starting point in application development. Which components to integrate depends on the requirements imposed on the application [94]. Given a platform, an application, which can be partially specified in software and partially in hardware, is mapped to the multi-processor platform, such that the timing requirements imposed on the application are satisfied.

#### **1.2** Manufacturing process variation

To reduce the power consumption of consumer electronics and decrease the area of integrated circuits, thus enabling integration of more functionality on a chip die, transistor feature sizes have traditionally been scaled down. An observation that the integration density of integrated circuits doubles approximately every two years was made by Gordon Moore in 1956. This observation, known as Moore's law [56, 57], still holds up to this day. However, scaling CMOS technology into nanometer feature size nodes has made it practically impossible to precisely control the manufacturing process. Major sources of manufacturing process variation are random dopant fluctuations and sub-wavelength lithography for patterning transistors [11]. Process variation results in variability in key design parameters, such as transistor channel length and threshold voltage, and interconnect width [12,61]. Parameter variability, in turn, influences circuit speed [13,20], power consumption and leakage [51]. Considerable variability of up to 50% in the longest path delay of a processor is reported in available literature [20,51]. Process variation can be categorized into *die-to-die* and *within-die* variations. Die-to-die variation acts globally on the entire chip die, affecting parameters of all devices (i.e. transistors) on the die identically. Die-to-die variation is seen between dies within a wafer and between dies of different wafers (due to wafer-to-wafer variation). In contrast, within-die variation affects parameters of devices on the same die differently. It can be classified into systematic and random components. Systematic within-die variation exhibits spatial correlation, such that nearby devices possess similar parameter values due to high correlation, which dies out quickly as a function of distance on a die [22]. Random within-die variation is purely random from device to device on a die. The impact of within-die variation is expected to worsen as technology scales. Both die-to-die and within-die variations impact the maximum supported frequency of hardware components inside an MPSoC. Different (identically designed) hardware components on the same die, as well as the same hardware component across different dies, can have different maximum supported frequencies.

As a solution to process-induced variations, circuits are conventionally implemented with conservative design margins, or guard-bands, to guarantee the target frequency of each hardware component in manufactured multi-processor chips. This is known as *worst-case design*. Circuit guard-banding is typically done by using corner-files during the design and verification stages. These files describe the worst-case and best-case delay values of standard-cells, corresponding to *slow and fast process corners*, respectively. Under worst-case design, design synthesis is performed for the slow process corner, while the fast process corner is used in the design verification stage to correct possible set-up timing violations. Corner files lack detailed information on within-die variation. Instead, on-chip timing variation margin is added during the design verification stage to account for within-die variation with a pessimistic assumption that all the devices within a die are performing according to their worst case under slow process conditions.

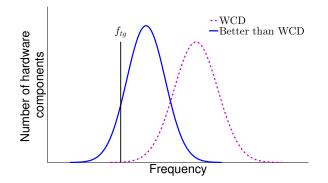

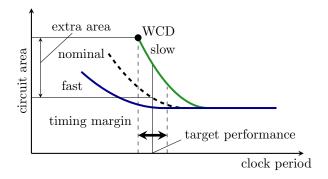

Figure 1.1 shows a qualitative example of the process-induced spread in frequency of a hardware component. As shown, almost all manufactured instances of the hardware component meet the target frequency  $f_{tg}$  under worst-case design (WCD). Therefore, from the perspective of an application, which can be partially defined in software and partially in hardware, the hardware components in a multi-processor platform have deterministic minimum frequencies, leading to a mapping of the application tasks to the hardware components in the multiprocessor platform, such that a certain timing requirement (e.g. throughput or latency) imposed on the application is satisfied. However, worst-case design has a considerable impact on circuit area, power consumption and leakage [33, 40]. Consider the qualitative circuit area and clock period trade-off curves for slow, nominal and fast process corners for a generic circuit, illustrated in Figure 1.2. As can be seen, larger circuit up-sizing is performed for a lower clock period (higher performance) under worst-case design. The added timing variation margin to account for within-die process variation also results in increased circuit area, as illustrated in the figure. Due to increased circuit area, power consumption and leakage, the benefits of technology scaling can be lost.

Figure 1.1: Process-induced spread in frequency of a hardware component for worst-case and better than worst-case designs, where  $f_{tg}$  is the target frequency.

**Figure 1.2:** Circuit area and clock period trade-off curves for slow, nominal and fast process corners. The timing margin accounting for within-die process variation is shown by an arrow.

### **1.3** Problem statement

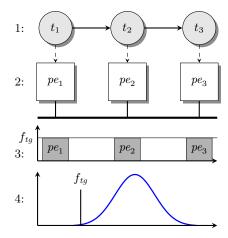

The trends outlined in Sections 1.1 and 1.2 show that the requirements on computational capability and low energy consumption of multimedia and wireless applications are increasing. Designers use multi-processor systems and platformbased design to deal with the increasing complexity of systems and to shorten time to market. As a solution to increasing process-induced variation in the frequency of hardware components in a multi-processor system, a worst-case design approach is adopted. This results in a considerable increase in circuit area and power consumption, and can lead to a loss in the benefits of technology scaling. This thesis deals with the design of real-time streaming applications constrained by a throughput requirement with reduced design margins, referred to as better than worst-case design. With better than worst-case design, the area, the power consumption and the leakage of a circuit are reduced. Smaller circuit area and thus die size results in a larger number of gross dies on a wafer. However, the target maximum supported frequency of hardware components in a multi-processor system is not guaranteed anymore. The spread in the maximum supported frequency of an example hardware component with respect to its target speed, under better than worst-case design, is illustrated in Figure 1.1. The goal of this thesis is to maximize the number of good dies that satisfy the throughput requirement of a real-time streaming application. This goal is accomplished by providing algorithms to exploit process-driven variation in frequency of hardware components in a multi-processor system in the application mapping and voltage-frequency island partitioning stages. The main concept of the work is illustrated in Figure 1.3, where an application with a throughput requirement is mapped to a multi-processor platform under both worst-case and better than worst-case designs. With worst-case design (Figure 1.3a), the target speed of the processing cores (denoted by pe) is guaranteed at the cost of large area. All processing cores are operated at their target speeds, providing sufficient computational capability for the application to satisfy its throughput requirement (for a given mapping). With better than worst-case design (Figure 1.3b), the area of the processing cores is reduced, but the target speed is not guaranteed anymore. However, there may be processing cores with higher and lower than the target speeds on the same chip die due to the impact of within-die variation. Operating the processing cores at their corresponding speeds and using the available mapping flexibility, the allocation of the tasks of an application to the processing cores can be tailored for each specific chip, such that the throughput requirement is satisfied whenever possible. This can result in a larger number of good dies, given that a larger number of gross dies are available on a wafer due to smaller die area.

The building blocks of this thesis are a multi-processor platform, a streaming application and a model of computation (MoC) that can capture a streaming multimedia or wireless application along with its mapping to a multi-processor platform. Using the model of computation, timing guarantees can be given by

$t_3$

performing design-time analysis. Due to process variation, the frequency of hardware components is given by a probability distribution. A network on chip provides interconnection between hardware components in the multi-processor system. The hardware components are partitioned into voltage-frequency islands. A set of clock-frequency levels are provided to each island. We introduce a metric termed *timing yield* quantifying the percentage of manufactured chips satisfying the throughput requirement imposed on an application. The number of good dies is given by the product of timing yield and the number of gross dies on a wafer. Therefore, the algorithms presented in this thesis aim at designing systems with high timing yield, such that the number of good dies is maximized.

$f_{tg}$

$pe_1$   $pe_2$   $pe_3$  $pe_1$   $pe_2$   $pe_3$  $f_{tg}$

(a) Worst-case design. The processing cores in the platform are operated at their target speeds (3:). For a certain mapping, the throughput requirement is satisfied.

(b) Better than worst-case design. There may be cores with higher and lower than the target speeds on a die (4:). The mapping can be adjusted for each specific chip, such that the throughput requirement is satisfied whenever possible. Given a larger number of dies on a wafer (smaller area (2:)), the number of good dies can be maximized.

Figure 1.3: An application (1:) constrained by a throughput requirement is allocated to a multi-processor platform (2:) under worst-case and better than worst-case designs.

### 1.4 Overview of solution

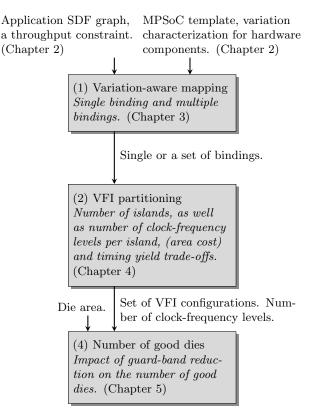

To address the problem in Section 1.3, this thesis proposes a design flow, called better than worst-case design. This section provides a brief overview of the flow. The design flow is shown in Figure 1.4. It assumes that a streaming application that has to be implemented on a multi-processor platform is modeled by a synchronous data-flow (SDF) graph [36,37]. SDF graphs are well-suited for modeling and analysis of streaming applications, and have multiple efficient techniques for throughput computation [79]. The hardware platform is a NoC-based multiprocessor platform with voltage-frequency islands, as introduced in Section 1.3. The SDF graph of the application includes information on the number of clock cycles it takes to execute each actor (modeling computation) on each processing element in the multi-processor platform and the amount of data sent between actors. This SDF model of the application is decoupled from the process-induced variation in the frequency of hardware components in the platform.

Figure 1.4: Design flow.

In Step 1 of the flow, the application is allocated to the platform, such that the timing yield is maximized. For this purpose, both exhaustive and heuristic mapping algorithms are proposed in this thesis. Two different mapping approaches are presented: *single-binding* and *multiple-bindings*. With the single binding mapping approach, only a single binding for all manufactured chips is derived. In contrast, with the multiple-bindings mapping approach, a set of bindings are selected for the manufactured chips. These bindings are stored and based on each manufactured

chip, a binding is selected at an initial run-time configuration stage, such that the throughput of the application is maximized. Multiple bindings always result in equal or higher timing yield. To compute the timing yield, a characterization of the hardware multi-processor platform in terms of possible clock-frequency sets for processing elements and the network on chip is performed. The probability that the processing elements and the network on chip are operated at a certain set of clock frequencies is computed. The throughput of the mapped application for the different clock frequency sets is analyzed by constructing another model of the application, which captures the resource allocation for the application on the platform. The actors in this graph are characterized by execution times in *seconds*. Therefore, this model of the application is not decoupled from the variation in frequency of hardware components.

From the first stage of the flow, a single or a set of bindings are derived that result in maximized timing yield. Using these bindings, trade-offs between the number of voltage-frequency islands, as well as the number of clock-frequency levels per island, and timing yield are performed in the second stage of the flow (Step 2). The higher the number of islands and clock-frequency levels per island, the higher the additional area (and power consumption) cost of clock-generation units associated with the islands is. Therefore, by reducing the number of islands, the die size becomes smaller, resulting in more gross dies on the wafer. On the other hand, a reduction in the number of voltage-frequency islands and clockfrequency levels for each island may lead to decreased timing yield. This thesis introduces heuristic algorithms to perform voltage-frequency island partitioning, such that the timing yield is maximized for a given number of islands. Algorithms considering both a single and multiple bindings are proposed. The result of the second stage of the flow is a set of voltage-frequency island configurations and a number of clock-frequency levels for the islands, such that high timing yield is provided.

In the final stage of the flow (Step 3), the change in the number of good dies due to reducing circuit guard-bands is evaluated. In this stage, the mapping of the application to the platform in terms of a single or a set of bindings, the set of voltage-frequency island configurations and the number of clock-frequency levels for each island are known. The number of good dies are evaluated for a set of guard-band reduction values, such that the reduction providing the highest number of good dies is selected. In this stage, characterization of variation in the frequency of hardware components for each guard-band reduction value must be provided. Additionally, the circuit (die) area reduction factor due to reduced guard-bands has to be known.

## 1.5 Contributions

This thesis makes five contributions to develop real-time streaming applications, constrained by a throughput requirement on a multi-processor system under bet-

ter than worst-case design (i.e. with reduced design margins).

- 1. A formal framework is presented to estimate the probability distribution of application throughput in a NoC-based multi-processor system with voltage-frequency islands in the presence of process-induced frequency variations of hardware resources (Chapter 2). Both within-die and die-to-die variations are considered. Any set of clock-frequency levels can be specified per VFI domain. We use synchronous data-flow (SDF) to model a streaming application mapped to an MPSoC. The novelty of our SDF formulation lies in the explicit modeling of software execution in terms of clock cycles (which is independent of the frequency variation of hardware components), and in terms of seconds (which does depend on the frequency variation of hardware components), which are linked by an explicit binding. This modeling allows a system designer to analyze the throughput of an application mapped to an MPSoC in the presence of process-driven variations. An earlier version of this work was published in [52–54].

- 2. Optimal and heuristic mapping algorithms are proposed to map streaming applications to a NoC-based multi-processor system with voltage-frequency islands under within-die and die-to-die process-driven variations (Chapter 3). We differentiate best-effort, firm real-time and soft real-time application classes, and define an optimization criteria for each of them. Single-binding and multiple-bindings mapping approaches are presented. With the single-binding mapping approach, a single binding for all manufactured chips is computed, while a set of bindings are derived with the multiple-bindings approach. At an initial run-time configuration stage, the right binding that maximizes throughput for a particular chip is selected. This work was published in [52, 53].

- 3. Heuristic algorithms to partition processing elements in a NoC-based multiprocessor system into voltage-frequency islands for maximized timing yield in the presence of die-to-die and within-die variations are presented (Chapter 4). Algorithms considering both a single and multiple bindings for manufactured chips are given. An earlier version of this work was published in [54]

- 4. A demonstration on case-studies is presented showing how the framework proposed in this thesis can be used to estimate the impact of reducing circuit design margins on the number of good dies that satisfy the throughput requirement of a real-time streaming application (Chapter 5). We show for both synthetic and several real applications that the proposed design flow can increase the number of good dies per wafer, compared to conventional worst-case design.

- 5. All the presented algorithms and the formal models have been implemented in C++ in the publicly available SDF For Free (SDF<sup>3</sup>) tool-kit [72,81].

2

## FORMAL MODELING

To analyze the performance of an application mapped to a multi-processor platform at design time, a model of computation is required. The model needs to capture the application, the platform and the mapping of the application to the platform. The impact of process variation on the hardware resources (i.e. processing elements, routers, network interfaces and links) in the platform also needs to be captured in the model. This chapter introduces the formal models that are used throughout this thesis. We start by defining a hardware multi-processor platform as a *platform graph*. We present how the modeling of variation in the maximum supported frequency of hardware resources due to process variation is performed. Based on this variation, a characterization of the platform graph in terms of possible clock-frequency sets for processing elements and the interconnect is performed. The methodology to compute the probability that the processing elements and the interconnect are operated at a certain set of clock frequencies is presented. Later, an SDF model of a streaming application, named a resourceaware application graph, is introduced. This model is unaware of the binding of application actors to processing elements, and is hence decoupled from hardware variation. Finally, we define another SDF model of the application, coined as a bound application graph. This graph captures the binding of a resource-aware application graph to a platform graph. We describe how resource allocation is modeled in a bound application graph. This model is used to perform timing analysis of the mapped application. While a resource-aware application graph describes performance in terms of execution time in cycles, the essence of a bound application graph is that it considers performance in terms of execution time in seconds. This allows us to take process-induced variation in the frequency of processing elements into account. The presented techniques are general and apply to

00

any system that implements the models described in this chapter. Examples of such systems are CoMPSoC [25], CA-MPSoC [73], Daedalus<sup>RT</sup> [5], MAMPS [34], and systems by NXP [59] and STE / Ericsson [84].

#### 2.1 Platform graph

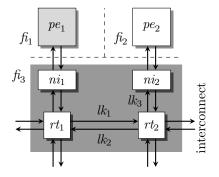

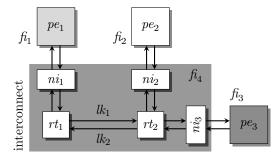

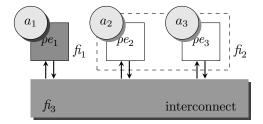

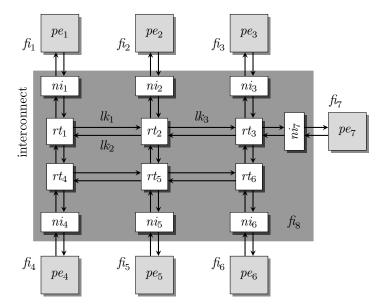

The template of a hardware multi-processor platform used in this thesis and referred to as a platform graph is illustrated in Figure 2.1. It consists of generic processing elements, such as processors, DSPs, or hardware accelerators, connected to each other by a network on chip (NoC), later referred in this thesis as an interconnect. Processing elements are denoted by pe. We assume an arbitrary topology interconnect, which consists of routers, denoted by rt, network interfaces, denoted by ni, and unidirectional links, denoted by lk. Routers are connected to each other and to network interfaces by links. The interconnect provides lossless and ordered data transmission. Each processing element is connected to a single network interface in the interconnect. It is assumed that the network interfaces sit close to processing elements, and that the connections between processing elements and network interfaces do not introduce any delay. The path from a network interface to another network interface in the interconnect is referred to as a connection. A connection provides a certain maximum bandwidth (in bytes per cycle) assuming that all resources on the connection are reserved. It also has a certain hop count, given by the number of routers on the path. For constructing a connection model in an application SDF graph, presented later in Section 2.5.1, we require that any arbitration point in a connection can be modeled as a *latency* rate server [78], independent of other connections. Note that any starvation free arbitration can be modeled by a latency rate server. Examples of interconnects that fulfill these requirements are [21, 26, 27, 32, 39, 50, 70, 77, 83, 89, 90, 92]. In this thesis we assume a time-division multiplexing (TDM) arbitration policy (although other arbitration policies can be used). The arbitration for the shared router network is performed in network interfaces, which packetize the transactions from the processing elements and inject them into the router network as flow control digits (flits). All network interfaces in the interconnect have the same slot table size (in number of slots). The injection of flits, regulated by the TDM tables, is done such that no two flits ever arrive at the same link at the same time. Therefore, the flits are forwarded without arbitration in the interconnect. Resource reservation on a connection is performed by allocating a number of slots in the TDM slot table. This provides a certain minimum bandwidth and maximum latency on the connection, as described in more details in Section 2.5.1. Network-on-chips that provide the described properties are Æthereal [26], Aelite [27], dAElite [77], Nostrum [50], SoCBUS [92], SurfNoC [89], and NoCs given in [70], [90], [21] and [83]. We formally define an interconnect in Definition 1. We refer to a processing element, a router, a network interface and a link in a platform graph as a (hardware) resource. As such, the union of the sets of processing elements, routers, network interfaces and links represents the set of all resources in the platform graph (Definition 2). The multi-processor platform is given by a globally asynchronous, locally synchronous (GALS) architecture [48], where the processing elements and the interconnect are partitioned into voltage-frequency islands (VFI). The interconnect is placed in an separate VFI, and thus the resources in the interconnect belong to that island. The set of voltage frequency islands is denoted by *FI*. Communication between the processing elements and the interconnect is accomplished by means of mixed-clock first-in-first-out (FIFO) buffers, which are part of network interfaces. In Figure 2.1, the separation between clock domains is shown by the dotted lines. A clock-generation unit (CGU) that provides a set of discrete clock-frequency levels, is dedicated to each voltage-frequency island. The formal definition of a platform graph gp is given in Definition 3. The set of all platform graphs is denoted by GP. The multi-processor platform depicted in Figure 2.1 is partitioned into three islands, namely  $f_{i_1}$  and  $f_{i_2}$  comprising processing elements  $pe_1$  and  $pe_2$ , respectively, and  $f_{i_3}$  consisting of the interconnect.

Figure 2.1: The template of a multi-processor platform consisting of processing elements connected to each other by an interconnect. The processing elements and the interconnect are placed in different voltage-frequency islands. The separation between clock domains is shown by the dotted lines.

**Definition 1.** (Interconnect) An interconnect noc is a 6-tuple  $\langle RT, NI, LK, \eta, sz_{tb}, sz_{fl} \rangle$  consisting of a set RT of routers, a set NI of network interfaces, a set LK of links connecting routers and network interfaces in an arbitrary topology, a TDM slot table size  $sz_{tb}$  (in number of slots) for all network interfaces, a flit size  $sz_{fl}$  (in bytes), a function  $\eta(n_i, n_j)$ , which for a connection from a network interface  $n_i \in NI$  to a network interface  $n_j \in NI$  ( $n_i \neq n_j$ ) returns a tuple  $\langle \beta, \Psi \rangle$  with  $\beta$  the maximum bandwidth (in bytes per cycle) assuming that all slots in the TDM table are reserved, and  $\Psi$  the number of hops.

**Definition 2.** (Set of resources) The set R of resources is the union of the sets PE of processing elements, RT of routers, NI of network interfaces, and LK of

links in a platform graph, and is defined as

$$R = PE \cup RT \cup NI \cup LK \tag{2.1}$$

**Definition 3.** (Platform graph) A platform graph gp is a 5-tuple  $\langle PE, noc, FI, \psi, \chi \rangle$ consisting of a set PE of processing elements, an interconnect noc, a set of voltagefrequency islands FI, a function  $\psi(fi) : FI \to \mathcal{P}(R)$ , which for each voltagefrequency island  $fi \in FI$  returns the set  $R_{fi} \in R$  of resources belonging to the island, and a function  $\chi(pe) : PE \to FI$ , which for each processing element  $pe \in PE$ returns the voltage-frequency island  $fi \in FI$  to which the processing element belongs. Each processing element  $pe \in PE$  is connected to a single network interface  $ni \in NI$  in the interconnect noc.

#### 2.2 Variation in hardware resources

In this section, we present the modeling of the impact of manufacturing process variation in the maximum supported frequencies of hardware resources in a platform graph. Manufacturing process variation can be classified into die-to-die and within-die variations. Die-to-die variation, also referred to as global variation, acts globally on the entire chip die, affecting parameters of all devices (i.e. transistors) and wires on the die identically. Global variation is seen between dies within a wafer and between dies of different wafers (due to wafer-to-wafer variation); therefore, overall global variation presumes multiple wafers. In contrast, within-die variation, also known as local variation, affects parameters of devices on the same die differently. It can be classified into systematic and random components. Systematic local variation exhibits spatial correlation, such that nearby devices possess similar parameter values due to high correlation, which dies out quickly at the level of devices on a die, as a function of distance [22]. While the parameter correlation between adjacent devices on a die is high, the correlation between larger adjacent logic blocks on a die, such as a processing element, is typically much lower. Furthermore, measurements performed by Pang et al. [64, 65] show no significant spatial correlation at 45 nm technology, in contrast to 90 nm technology. This is partially because random local variation, which is purely random from device to device, has more than doubled at 45 nm technology whereas systematic local variation has decreased. For simplicity, we assume zero correlation between maximum supported frequencies of processing elements, routers, network interfaces and links in a chip due to local variation. An extension of the models presented in this section, such that correlation between maximum supported frequencies can be specified, is one of the possible future works of this thesis. It has been shown that a normal distribution is a good fit for modeling the impact of global and local manufacturing process variations [13, 64]. We, therefore, use normal distributions to model the impact of global and local process

variations in the maximum supported frequency of resources in a platform graph. We thus proceed by presenting the models.

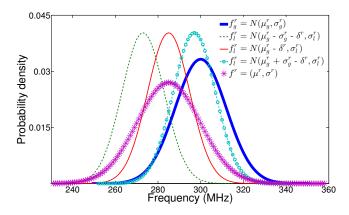

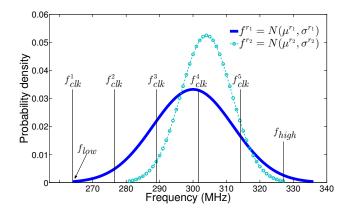

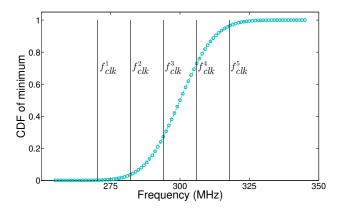

#### 2.2.1 Global variation