# Efficient In-Situ Delay Monitoring for Chip Health Tracking

Hadi Ahmadi Balef

Committee:

prof.dr. K.G.W. Goossens prof.dr. J. Pineda de Gyvez prof.dr.ir. P.G.M. Baltus dr. S.D. Cotofana prof.dr. M. Baradaran Tahoori prof. dr. H. Corporaal Eindhoven University of Technology, 1<sup>e</sup> promotor Eindhoven University of Technology, 2<sup>e</sup> promotor Eindhoven University of Technology, chairman Technische Universiteit Delft Karlsruhe Institute of Technology Eindhoven University of Technology

© Hadi Ahmadi Balef 2019. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

This thesis is typeset in LATEX, was written in Sublime Text and built with SCons.

Printed by ProefschriftMaken – The Netherlands.

A catalogue record is available from the Eindhoven University of Technology Library. ISBN: 978-90-386-4930-6

# Efficient In-Situ Delay Monitoring for Chip Health Tracking

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op vrijdag 13 december 2019 om 11:00 uur

door

Hadi Ahmadi Balef

geboren te Ray, Iran

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

| voorzitter:              | prof.dr.ir. P.G.M. Baltus                                         |

|--------------------------|-------------------------------------------------------------------|

| 1 <sup>e</sup> promotor: | prof.dr. K.G.W. Goossens                                          |

| 2 <sup>e</sup> promotor: | prof.dr. J. Pineda de Gyvez                                       |

| leden:                   | prof.dr. M. Baradaran Tahoori (Karlsruhe Institute of Technology) |

|                          | dr. S. D. Cotofana (Technische Universiteit Delft)                |

|                          | prof.dr. H. Corporaal                                             |

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

Dedicated to my lovely wife, Hamideh

He who does not thank the people is not thankful to Allah.

- Prophet Muhammad

#### ACKNOWLEDGMENTS

# "Glory be to Him Who has subjected this to us otherwise, we could never have accomplished this."

This thesis is the result of a four-year development process during which many people helped me.

First of all, I thank my first promoter, Kees Goossens, for giving me the opportunity to work on my PhD project, and trusting me. His supportive approach has been a blessing for me and his meticulous way of working not only helped me to improve the quality of this work but also helped me to develop some habits that will improve the quality of my future works. Furthermore, I would like to thank my second promoter, José Pineda de Gyvez, for sharing his priceless wisdom and experience with me generously. José has always been available for me when I wanted to discuss new ideas with him. He also gave me the chance to work at NXP Semiconductors. Many thanks to Hamed Fatemi for hosting me at NXP Semiconductors for more than two years, allowing me to have a real sense of the semiconductor industry. In addition, I would like to extend my gratitude to the members of my defense committee, Sorin Cotofana from the Delft University of Technology, Mehdi Tahoori from the Karlsruhe Institute of Technology, and Henk Corporaal from the Eindhoven University of Technology,

My PhD research is conducted at Electronic Systems group, working with many good colleagues. I had the opportunity to do two tapeouts in my project and doing these tapeouts and performing the experiments would not be achievable without helps from Andrew Nelson (RTL design), Mark Wijtvliet (PCB design), and Martijn Koedam (laboratory instruments). Having Kamlesh Singh and Paul Detterer was very valuable for me as we could learn a lot of things together. I also thank Hailong Jiao for helping me a lot in the beginning of my PhD project as my daily supervisor. I am grateful to the secretaries of the group, Marja and Feyza, for their kindness and cares. I have also enjoyed being together with other people in the group. Thank you Alessandro, Ali, Amr, Barry, Cumhur, Emad, Gabriela, Hamideh, Juan, Luc, Mahdi, Mahsa, Majid, Mojtaba, Rasool, Reinier, Sahar, Sajid, Shayan, Shima, Shubhendu, Sven, Victor, Yonghui, and Zhan.

I would like to also thank people from outside my professional environment for supporting me during these years of being far from home. Thank you Hamid Pourshaghaghi, Mohammad Tahghighi, Esmaeil Najafi, and all other people in our Iranian community. Special thank goes to my dear friend, Sobhan Niknam, who we could have very joyful times together. A very special thank is in place for my parents, Hooshang and Shirin, who helped me to develop myself into who I am now. I would like to also mention my brother, thank you Dash Hooman! I also thank my wife's family for being strong support for us. I am very thankful to have my cute and sweet daughter, Helena, as she could make cheerful moments in my life.

And last, but foremost, my lovely wife, Hamideh. You gave me the energy and motivation and without your love and support, this PhD would not have been the same. You shared with me the difficult and the good times. Thank you very much for your patience and endurance.

> Eindhoven, November 2019 Hadi Ahmadi Balef پادی احمدی بالف

# SUMMARY

# Efficient In-Situ Delay Monitoring for Chip Health Tracking

The growing use of digital integrated circuits in safety-critical applications together with variability issues of the technology scaling trends necessitate reliability awareness in digital circuits. Timing is one of the main concerns for the reliability of digital circuits as correct timing is important for the correct operation of the circuits. This thesis investigates techniques to realize an efficient and reliable chip health tracking technique based on monitoring circuit timing.

Continuous tracking of chip health status is essential to minimize the risk of failure. Therefore, the demanding chip-health tracking technique must be real-time, i.e., it should run in parallel to the main workload and it must predict failure. Besides, to make sure that the chip-health tracking system is reliable itself, it must provide enough coverage of critical circuit components. Otherwise, it fails to report a problem in the system. The technique must be also cost-efficient to make sure that the benefits of technology scaling are preserved. Moreover, the proposed solution must be able to be integrated into the standard IC design flow.

Based on these requirements, the main goal of this thesis is to develop an efficient technique for timing reliability of digital circuits. Following this goal, some contributions are made in this thesis.

**More Accurate Timing Model**: Accurate modeling of circuit timing and its unreliability effects are essential for developing a well-founded chip health tracking technique. A novel timing model is proposed for sequential components of the digital circuit (i.e., flip-flops). The proposed model takes the inter-dependency of timing constraints into account with more accuracy and less characterization effort and it is integrated into the timing analysis flow. Moreover, a new procedure is proposed for modeling the timing unreliability in standard IC design and timing analysis tools.

**Effective In-Situ Delay Monitoring**: In-situ delay monitoring is an advanced technique to sense timing slacks. A new in-situ delay monitoring technique is proposed in this thesis that inserts the monitors at particular circuit nodes to achieve cost reduction and increase coverage. With the new technique, the cost per monitor and the number of monitors are reduced, and the coverage and protectiveness of slack monitoring are improved.

**Novel Chip-Health Tracking System**: In sharp contrast to the conventional deterministic approach that does not take advantage of the underlying hardware in the most efficient way, a new chip health tracking is proposed which is based on a probabilistic approach. The probability of monitor excitation is captured as an indication of slack values and delay degradation. Hence, by analyzing the monitor excitation rate, more information about delay degradation is extracted from each in-situ delay monitor.

Within-Cycle Error Avoidance Technique: A new timing speculation system is proposed in this thesis that masks the detected faults and avoids timing errors within one clock cycle. This error avoidance is necessary for increasing the reliability of the proposed chip health tracking technique for safety-critical applications. In this way, the failure risk is minimized by avoiding the occurrence of timing errors.

# CONTENTS

| 1 | INTRODUCTION<br>1.1 Reliability of Digital ICs                | 1<br>3 |

|---|---------------------------------------------------------------|--------|

|   | 1.2 Problem Statement                                         | 7      |

|   | 1.3 Requirements                                              | 8      |

|   | 1.4 State of the Art                                          | 9      |

|   | 1.5 Approach and Contributions                                | 14     |

|   | 1.6 Thesis Outline                                            | 16     |

| 2 | MODELING CIRCUIT TIMING AND ITS UNRELIABILITY                 | 17     |

|   | 2.1 Introduction                                              | 17     |

|   | 2.2 Timing of Digital Circuits                                | 18     |

|   | 2.3 Gradual Timing Degradation Effects                        |        |

|   | 2.4 Novel Modeling of Circuit Timing and Its Unreliability    | 24     |

|   | 2.5 Experimental Results for The Proposed Ideas               | 34     |

|   | 2.6 Summary                                                   | 37     |

| 3 | IN-SITU DELAY MONITORING ALONG TIMING PATHS                   | 39     |

|   | 3.1 Introduction                                              | 39     |

|   | 3.2 Preliminaries and Related Works                           | 39     |

|   | 3.3 In-situ Delay Monitoring Within Timing Paths              | 41     |

|   | 3.4 Analysis of Insertion Point Selection                     | 47     |

|   | 3.5 Experimental Results                                      | 50     |

|   | 3.6 Summary                                                   | 57     |

| 4 | STATISTICAL IN-SITU DELAY MONITORING FOR EFFECTIVE CHIP HEALT | н      |

|   | TRACKING                                                      | 59     |

|   | 4.1 Introduction                                              | 59     |

|   | 4.2 Preliminaries and Related Works                           | 60     |

|   | 4.3 The Proposed Chip-Health Tracking System                  | 61     |

|   | 4.4 The Monitors                                              | 63     |

|   | 4.5 The Signature Extractor                                   | 64     |

|   | 4.6 Experimental Results                                      | 67     |

|   | 4.7 Summary                                                   | 70     |

| 5 | WITHIN-CYCLE ERROR PREVENTION FOR TIMING RESILIENCE           | 71     |

|   | 5.1 Introduction                                              | 71     |

|   | 5.2 Related Works                                             | 72     |

|   | 5.3 The Proposed Timing Speculation System                    | 73     |

|   | 5.4 Inspection Window and OR-tree Delay                       | 74     |

|  | xii | CONTENTS |

|--|-----|----------|

|--|-----|----------|

|    | 5.5   | Experimental Results                      | 75  |

|----|-------|-------------------------------------------|-----|

|    | 5.6   | Summary                                   | 79  |

| 6  | SILI  | CON IMPLEMENTATION                        | 81  |

|    | 6.1   | Introduction                              | 81  |

|    | 6.2   | Tape-out 1: Chip-Health Tracking          | 81  |

|    | 6.3   | Tape-out 2: Within-Cycle Error Prevention | 91  |

|    | 6.4   | Summary                                   | 103 |

| 7  | CON   | CLUSIONS AND FUTURE WORK                  | 105 |

|    | 7.1   | Conclusions                               | 105 |

|    | 7.2   | Future work                               | 110 |

| BI | BLIO  | GRAPHY                                    | 112 |

| A  | COD   | E LISTINGS                                | 123 |

| в  | CON   | IPSOC ARCHITECTURE                        | 127 |

| С  | LIST  | T OF ACRONYMS                             | 128 |

| D  | LIST  | T OF SYMBOLS                              | 129 |

| Е  | CUR   | RICULUM VITAE                             | 133 |

| LI | ST ОІ | PUBLICATIONS                              | 134 |

# LIST OF FIGURES

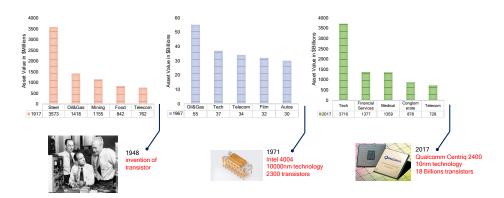

| Figure 1.1     | America's largest firms by sector in 1917, 1967, and 2017 [1].                                                                        | 2    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|------|

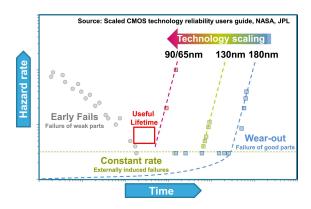

| Figure 1.2     | The effect of technology scaling on the failure rate bathtub curve [2]                                                                | 3    |

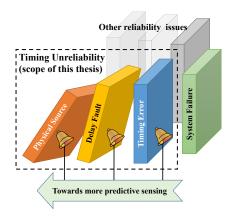

| Figure 1.3     | Cause-and-effect chain of timing unreliability.                                                                                       | 5    |

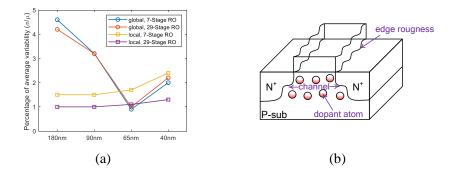

| Figure 1.4     | Variation effects. (a) The effect of process variations on inverter-<br>based ROs with 7 and 29 stages in different technology nodes. |      |

|                | (b) Cross-section of a transistor illustrating the roughness in<br>the channel edges and the randomly placed dopant atoms in-         |      |

|                | side channel.                                                                                                                         | 7    |

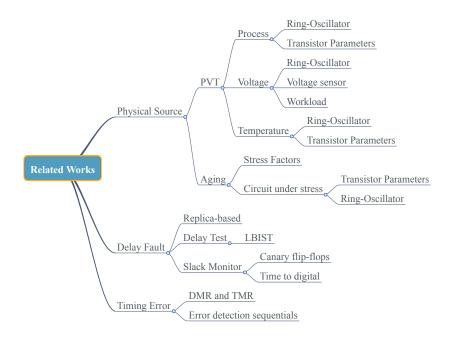

| Figure 1.5     | The categorization of state of the art works in timing unrelia-                                                                       | 10   |

| Eigene 1 (     | bility monitoring.                                                                                                                    | 10   |

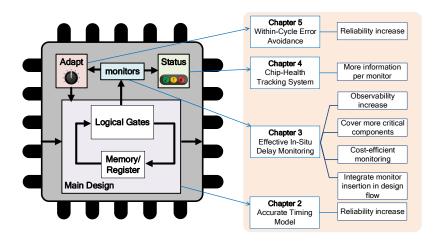

| Figure 1.6     | Thesis contributions.                                                                                                                 | 14   |

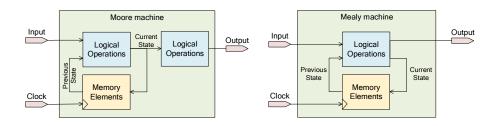

| Figure 2.1     | Mealy and Moore Finite State Machines.                                                                                                | 18   |

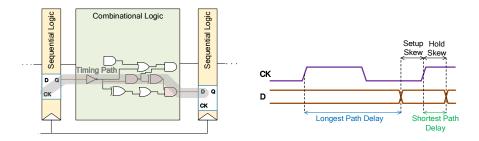

| Figure 2.2     | The circuit timing model. (a) timing path, and (b) waveforms                                                                          | 10   |

| <b>F</b> ' 0.0 | at the destination flip-flop.                                                                                                         | 19   |

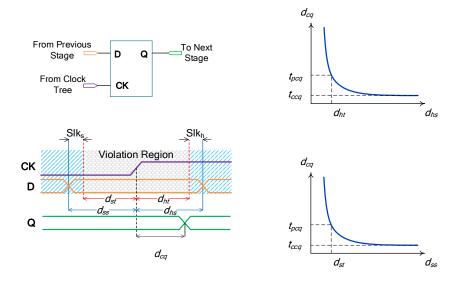

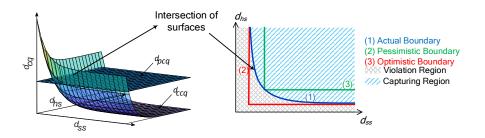

| Figure 2.3     | Timing definitions at a flip-flop.                                                                                                    | 21   |

| Figure 2.4     | The definition of setup/hold-time interdependency curve                                                                               | 21   |

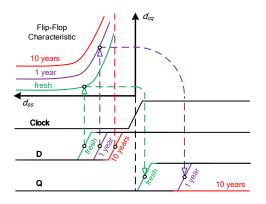

| Figure 2.5     | Effect of aging on the delay of a flip-flop.                                                                                          | 24   |

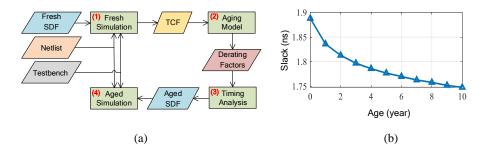

| Figure 2.6     | The aging simulation framework: (a) The flow of performing netlist simulation for the aged circuit. (b) The critical path slack       |      |

|                | in the typical corner considering aging for ARM Cortex M0                                                                             |      |

|                | with 200MHz speed constraint.                                                                                                         | 25   |

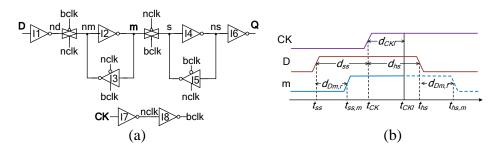

| Figure 2.7     | A master-slave flip-flop. (a) The circuit schematic. (b) The wave-                                                                    | 20   |

|                | forms at the input D and the middle point m, obtained based                                                                           |      |

|                | on the shortest and longest paths to capture a rising input                                                                           | 27   |

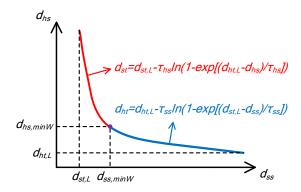

| Figure 2.8     | Illustration of the proposed setup/hold-time interdependency                                                                          |      |

|                | model and its parameters.                                                                                                             | 29   |

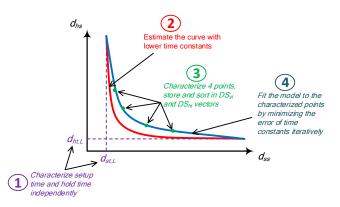

| Figure 2.9     | Illustration of steps to find the parameters of the proposed                                                                          |      |

|                | model for setup/hold-time interdependency.                                                                                            | 31   |

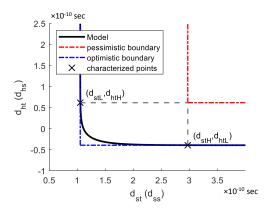

| Figure 2.10    | The setup/hold-time inter-dependency curve obtained with the model and a standard characterization tool for a flip-flop from          |      |

|                | an industrial 40nm library.                                                                                                           | 33   |

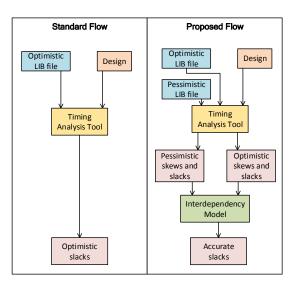

| Figure 2.11    | The standard timing analysis flow and the proposed timing                                                                             |      |

| 0              | analysis flow which also considers the interdependency of setup/h                                                                     | old- |

|                | time.                                                                                                                                 | 34   |

|                |                                                                                                                                       |      |

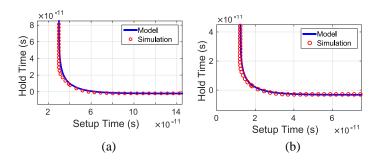

| Figure 2.12 | The setup/hold-time inter-dependency curve for data and clock                                      |      |

|-------------|----------------------------------------------------------------------------------------------------|------|

|             | input slopes of 50ps at (a) slow corner (Process:SS, $V_{DD} = 0.99V$ ,                            |      |

|             | T=125° <i>C</i> ) and (b) fast corner (Process:FF, $V_{DD} = 1.21V$ , T=0° <i>C</i> ).             | 35   |

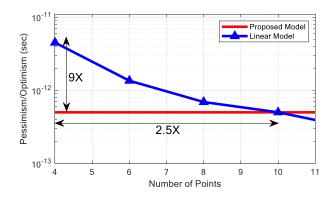

| Figure 2.13 | The pessimism/optimism of the model compared to the lin-                                           |      |

|             | ear approximation. With four characterization points, the pro-                                     |      |

|             | posed method has the same pessimism/optimism that the lin-                                         |      |

|             | ear approximation has with 10 characterization points (2.5X                                        |      |

|             | more computation efficiency).                                                                      | 36   |

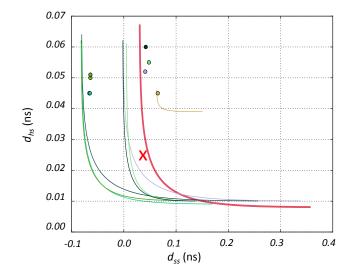

| Figure 2.14 | The setup/hold-time inter-dependency curve and the setup/hold-                                     |      |

|             | skew point for nine critical flip-flops (distinguished by color)                                   |      |

|             | for which the inter-dependency should be taken into account.                                       |      |

|             | One flip-flop (shown by the cross and red color) is marked to                                      |      |

|             | be failing according to the analysis.                                                              | 38   |

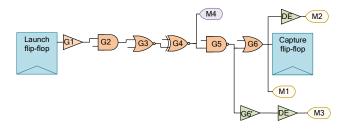

| Figure 3.1  | The insertion points of monitors along the timing paths of dig-                                    |      |

| C           | ital circuits for different in-situ delay monitoring techniques.                                   | 40   |

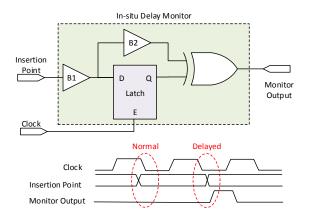

| Figure 3.2  | The design of in-situ monitor.                                                                     | 42   |

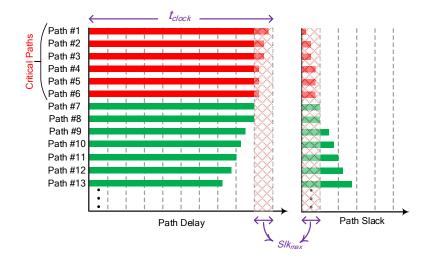

| Figure 3.3  | The definition of critical paths based on <i>Slk<sub>max</sub></i>                                 | 43   |

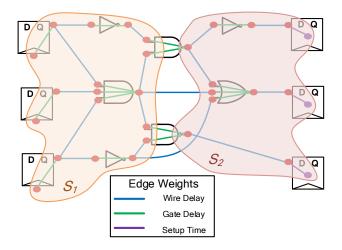

| Figure 3.4  | An example circuit graph showing the cut $C = (S_1, S_2)$                                          | 44   |

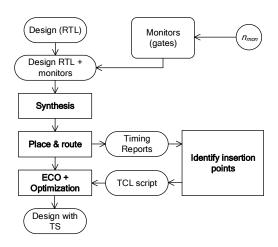

| Figure 3.5  | The proposed implementation flow.                                                                  | 46   |

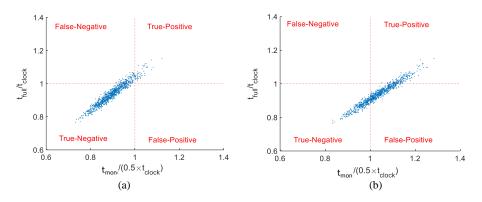

| Figure 3.6  | Scatter plot obtained from Monte Carlo simulations of a critical                                   |      |

| -           | path delay of an industrial design showing $t_{full}$ versus $t_{mon}$ for                         |      |

|             | the cases where (a) $t_{mon} = 0.5 \times t_{clock}$ , and (b) $t_{mon} = 0.55 \times t_{clock}$ . | 48   |

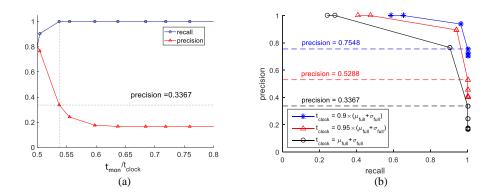

| Figure 3.7  | The effect of $t_{mon}$ on the precision and recall metrics (a) precision                          |      |

| -           | and <i>recall</i> versus $t_{mon}$ normalized to $t_{clock} = \mu_{full} + \sigma_{full}$ The      |      |

|             | maximum precision subject to no False-Negative prediction (recal                                   | l=1) |

|             | is 0.3367 (b) precision versus recall considering different t <sub>clock</sub>                     |      |

|             | In a better-than-worst-case design (smaller $t_{clock}$ ) the precision                            |      |

|             | of the monitor outputs increases.                                                                  | 49   |

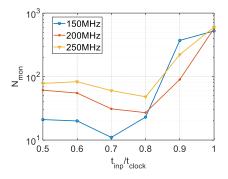

| Figure 3.8  | The number of monitors versus delay up to insertion point nor-                                     |      |

| -           | malized to $t_{clock}$ for the ARM Cortex M0. The core was designed                                |      |

|             | targeting different frequencies, considering $Slk_{max} = 0.1 \times t_{clock}$ .                  | 52   |

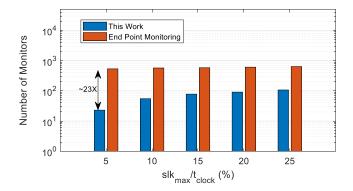

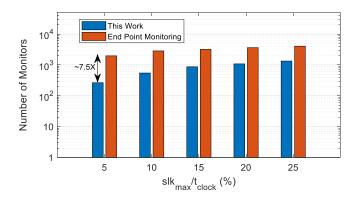

| Figure 3.9  | Comparison between the number of monitors with our tech-                                           |      |

|             | nique $(t_{mon} = 0.7 \times t_{clock})$ and the number of monitored end-                          |      |

|             | points for an ARM Cortex M0 processor considering different                                        |      |

|             | $Slk_{max}$ values normalized to the $t_{clock}$ .                                                 | 52   |

| Figure 3.10 | The histogram of slacks of monitors as well as the main flip-                                      |      |

| -           | flops for ARM Cortex M0 design targeting 200MHz speed with                                         |      |

|             | 64 monitors considering (a) $t_{mon} = 0.6 \times t_{clock}$ , and (b) $t_{mon} =$                 |      |

|             | $0.7 \times t_{clock}$ .                                                                           | 54   |

|             |                                                                                                    |      |

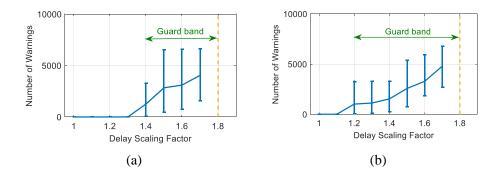

| Figure 3.11 | The number of cycles with warnings generated by the mon-                                                                                             |    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | itors versus the delay degradation factor. Results are of four                                                                                       |    |

|             | applications obtained based on a netlist simulation for 10K cy-                                                                                      |    |

|             | cles with timing annotation at the typical corner and scaling                                                                                        |    |

|             | the delays. The insertion points of 64 monitors are identified                                                                                       |    |

| Figure 3.12 | considering (a) $t_{mon} = 0.6 \times t_{clock}$ , and (b) $t_{mon} = 0.7 \times t_{clock}$ Comparison between the number of monitors with our tech- | 55 |

| -           | nique $(t_{mon} = 0.7 \times t_{clock})$ and the number of monitored end-                                                                            |    |

|             | points for an ARM Cortex M3 processor considering different                                                                                          |    |

|             | $Slk_{max}$ values normalized to the $t_{clock}$ .                                                                                                   | 56 |

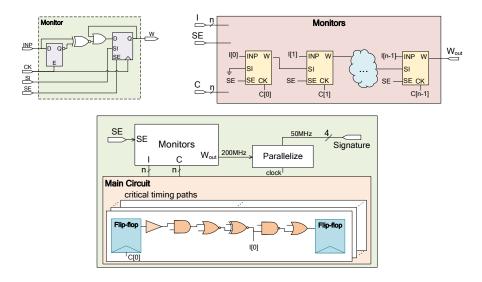

| Figure 4.1  | The proposed idea for chip-health tracking based on dynamic                                                                                          |    |

|             | in-situ monitoring.                                                                                                                                  | 61 |

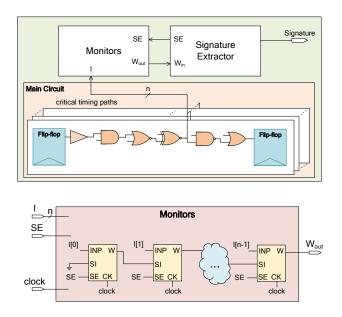

| Figure 4.2  | The proposed chip-health tracking system and the Monitors                                                                                            |    |

|             | block which consists of the monitors connected in a scan chain.                                                                                      | 62 |

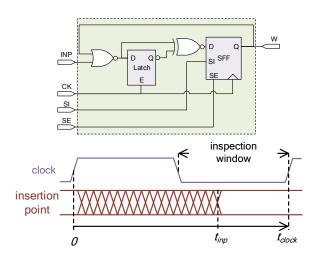

| Figure 4.3  | The design of monitor and activity of monitor insertion point.                                                                                       | 64 |

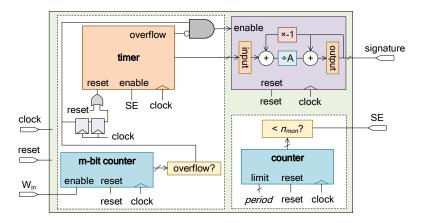

| Figure 4.4  | The design of signature extractor.                                                                                                                   | 65 |

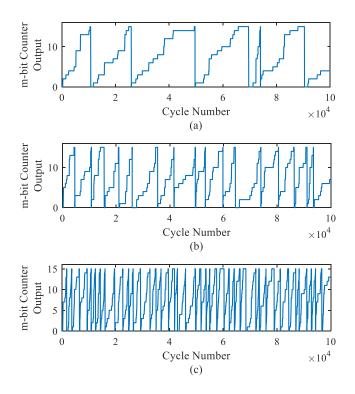

| Figure 4.5  | The output of the <i>m</i> -bit counter before overflow detector con-                                                                                |    |

|             | sidering three delay scaling factors (a) 1.4X, (b) 1.5X, and (c)                                                                                     |    |

|             | 1.6X                                                                                                                                                 | 68 |

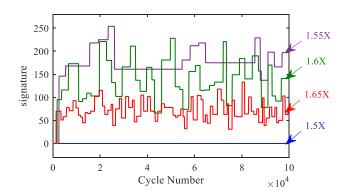

| Figure 4.6  | The signature considering different delay scaling factors                                                                                            | 68 |

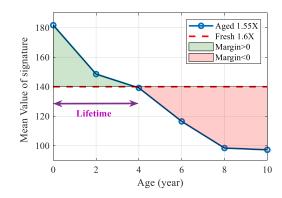

| Figure 4.7  | The averaged signature versus age with 1.55X delay scaling                                                                                           |    |

|             | and the lifetime based on the signature with fresh 1.6X delay                                                                                        |    |

|             | scaling                                                                                                                                              | 69 |

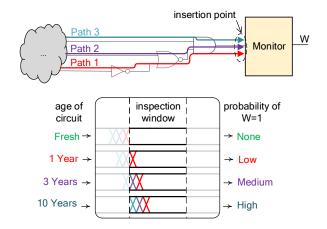

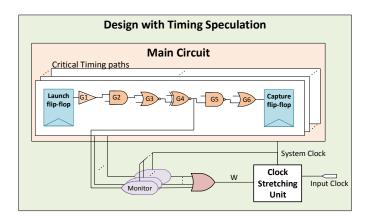

| Figure 5.1  | A high-level view to the proposed timing speculation technique.                                                                                      | 74 |

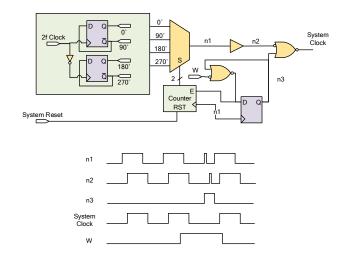

| Figure 5.2  | The design of clock stretching unit in the proposed timing spec-                                                                                     |    |

|             | ulation technique.                                                                                                                                   | 75 |

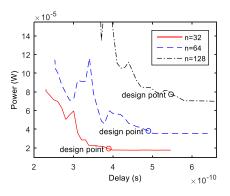

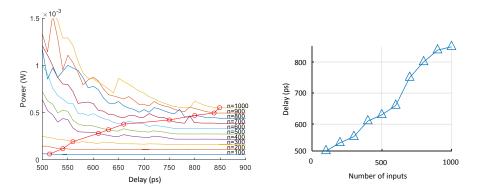

| Figure 5.3  | The power versus delay of the OR-tree considering the differ-                                                                                        |    |

|             | ent number of inputs, n. The design point is selected consid-                                                                                        |    |

|             | ering 10% increase in the power compared to the power when                                                                                           |    |

|             | the delay is relatively long.                                                                                                                        | 76 |

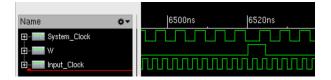

| Figure 5.4  | Netlist simulation waveforms showing System Clock being stretch                                                                                      | ed |

|             | by the clock stretching unit in response to a warning signal, W,                                                                                     |    |

|             | generated by the monitors                                                                                                                            | 76 |

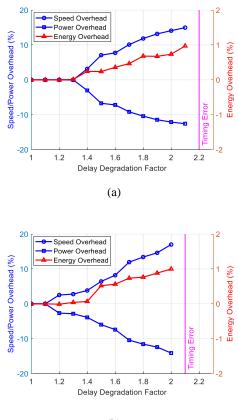

| Figure 5.5  | Speed, power, and energy penalty due to clock stretching ver-                                                                                        |    |

|             | sus the delay degradation obtained from a netlist simulation of                                                                                      |    |

|             | 10K cycles with timing annotation in the typical corner. The                                                                                         |    |

|             | insertion points of 64 monitors are identified considering (a)                                                                                       |    |

|             | $t_{mon} = 0.6 \times T$ , and (b) $t_{mon} = 0.7 \times T$                                                                                          | 78 |

# xvi list of figures

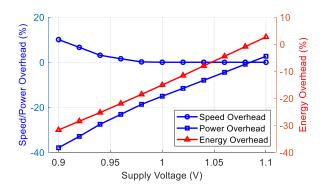

| Figure 5.6  | Speed, power, and energy overheads due to clock stretching<br>versus supply voltage obtained from a netlist simulation of 10K<br>cycles with timing annotation in the typical corner. The inser-                                                                                                                                          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | tion points of 64 monitors are identified considering $t_{mon} = 0.6 \times T$                                                                                                                                                                                                                                                            |

| Figure 5.7  | Delay of OR-tree versus the number of inputs based on the power-delay characteristic.                                                                                                                                                                                                                                                     |

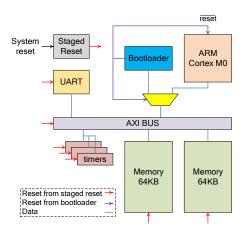

| Figure 6.1  | The architecture of the single-core microprocessor platform that is generated with CompSOC flow                                                                                                                                                                                                                                           |

| Figure 6.2  | The design and insertion point of the in-situ monitor in tape-<br>out 1.8                                                                                                                                                                                                                                                                 |

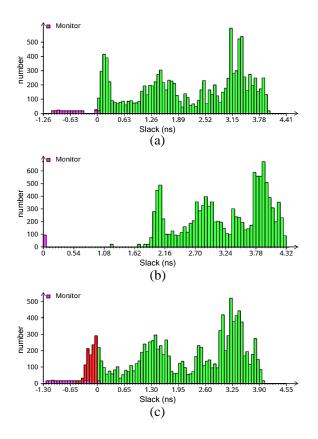

| Figure 6.3  | The slack histogram for (a) the slow corner, (b) the typical pro-<br>cess corner at nominal voltage (1.1V), and (c) the typical pro-<br>cess corner with lowered supply voltage to 0.9V                                                                                                                                                   |

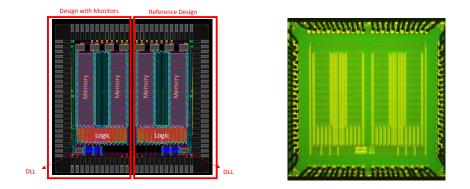

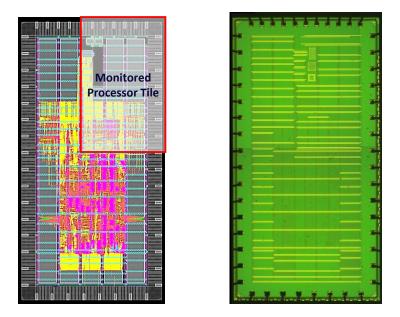

| Figure 6.4  | The layout and the die micro-graph of the first tape-out.                                                                                                                                                                                                                                                                                 |

| Figure 6.5  | The evaluation board for tape-out 1                                                                                                                                                                                                                                                                                                       |

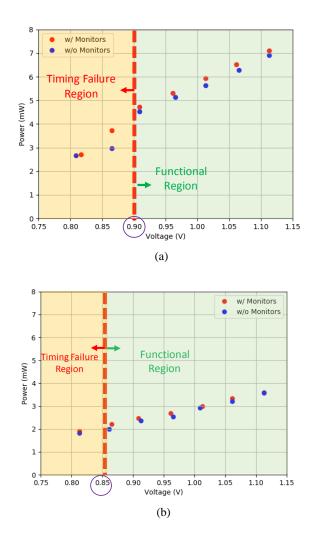

| Figure 6.6  | The total power consumption of the monitored and reference                                                                                                                                                                                                                                                                                |

| rigure 0.0  | platforms versus the supply voltage at (a) 200MHz, and (b) 100MHz.                                                                                                                                                                                                                                                                        |

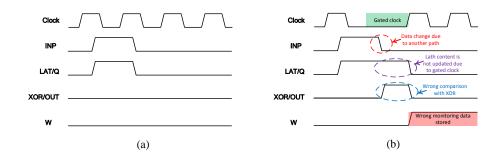

| Figure 6.7  | Example waveforms to illustrate the design issue with tape-out<br>1 due to automatic clock gating insertion during logic synthe-<br>sis. (a) The expected functionality of the monitor without the<br>gated clock signal, and (b) wrong information is stored in the<br>monitor due to the gated clock signal                             |

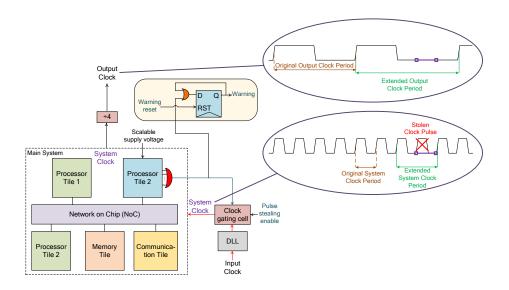

| Figure 6.8  | Architecture view to the taped out idea in a multi-processor<br>platform generated from CompSOC flow                                                                                                                                                                                                                                      |

| Figure 6.9  | The layout and the die micro-graph of the second tape-out 9                                                                                                                                                                                                                                                                               |

| Figure 6.10 | The evaluation board for tape-out 2                                                                                                                                                                                                                                                                                                       |

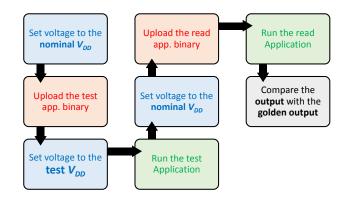

| Figure 6.11 | The flow of running experiments                                                                                                                                                                                                                                                                                                           |

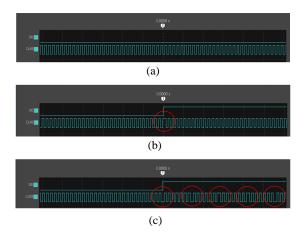

| Figure 6.12 | The effect of voltage scaling on the waveforms of the output clock of chip (with proper signal acquisition settings to digitize the waveforms): (a) at nominal voltage when no clock pulse stealing occurs, (b) at the voltage which the clock pulse stealing starts, and (c) at a lower voltage when clock pulses are stolen more often. |

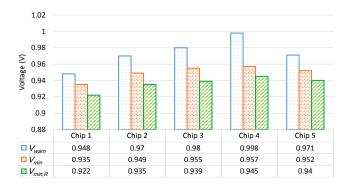

| Figure 6.13 | The effect of process variations on $V_{min}$ , $V_{min,R}$ , and $V_{warn}$ 9                                                                                                                                                                                                                                                            |

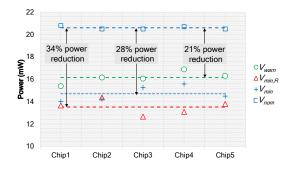

| Figure 6.14 | The effect of process variations on the power of the chip at $V_{min}$ , $V_{min,R}$ , $V_{warn}$ , and $V_{nom}$                                                                                                                                                                                                                         |

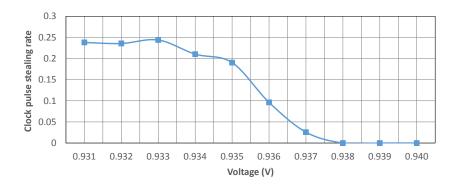

| Figure 6.15 | The CPSR of the first sample versus supply voltage value for         chip 1.       9                                                                                                                                                                                                                                                      |

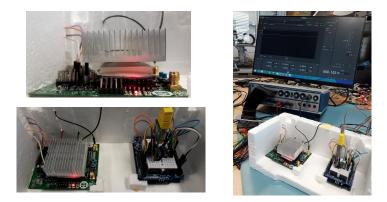

| Figure 6.16 | The setup to test the IC at high temperature                                                                                                                                                                                                                                                                                              |

| The climatic chamber to decrease the temperature                                  | 100                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

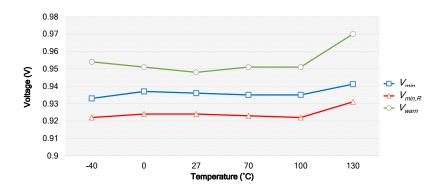

| The effect of temperature on $V_{min}$ , $V_{min,R}$ , and $V_{warn}$ for chip 1. | 101                                                                                                                                                                                  |

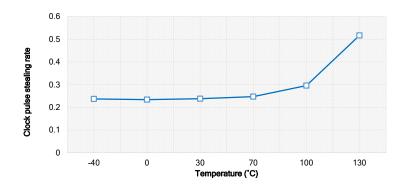

| The effect of temperature on CPSR at $V_{min}$ as an indicator of                 |                                                                                                                                                                                      |

| timing degradation for chip 1                                                     | 101                                                                                                                                                                                  |

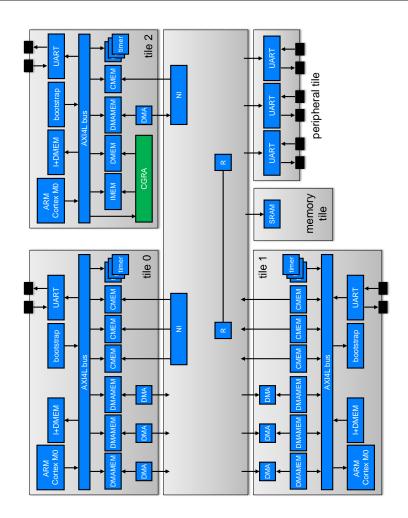

| The architecture if taped out multi-core microprocessor plat-                     |                                                                                                                                                                                      |

| form generated with CompSOC flow.                                                 | 127                                                                                                                                                                                  |

|                                                                                   | The effect of temperature on $V_{min}$ , $V_{min,R}$ , and $V_{warn}$ for chip 1.<br>The effect of temperature on CPSR at $V_{min}$ as an indicator of timing degradation for chip 1 |

# LIST OF TABLES

| Table 1.1 | Assessment of the state-of-the-art works in timing unreliabil-<br>ity monitoring based on the set of requirements for the de- |     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|           | manding chip health tracking system.                                                                                          | 13  |

| Table 2.1 | The maximum error of model with regard to the actual curve                                                                    | 15  |

| 1abic 2.1 | characterized with extensive SPICE simulations at different cor-                                                              |     |

|           | ners relative to input slope for input slopes ranging from 10ps                                                               |     |

|           | to 100ps.                                                                                                                     | 35  |

| Table 3.1 | The runtime of path-based and the proposed method to iden-                                                                    |     |

|           | tify monitor insertion points, considering $Slk_{max} = 0.1 \times t_{clock}$ ,                                               |     |

|           | for different ICT benchmark circuits synthesized for 1GHz clock                                                               |     |

|           | frequency                                                                                                                     | 50  |

| Table 3.2 | The implemented ARM Cortex M0 design specifications.                                                                          | 51  |

| Table 3.3 | Design overhead, monitored slack, and the number of moni-                                                                     |     |

|           | tored flip-flops with the proposed technique employed in an                                                                   |     |

|           | ARM Cortex M0 designed with a 200MHz speed target                                                                             | 53  |

| Table 3.4 | Comparing the proposed technique with LBIST technique for                                                                     |     |

|           | detection of timing degradation in a large industrial design. $\ .$                                                           | 57  |

| Table 4.1 | The design parameters of the proposed chip health tracking                                                                    |     |

|           | technique                                                                                                                     | 66  |

| Table 6.1 | The power measurements at the nominal voltage and two run-                                                                    |     |

|           | ning frequencies for the first tape-out.                                                                                      | 89  |

| Table 6.2 | The power measurements for the second tape-out                                                                                | 95  |

| Table 6.3 | The effect of changing the running application on $V_{min}$ , $V_{min,R}$ ,                                                   |     |

|           | $V_{warn}$ , and clock pulse stealing rate at $V_{DD} = V_{min}$ for chip 1                                                   | 99  |

| Table 6.4 | The effect of aging on $V_{min,R}$ , $V_{min,R}$ , $V_{warn}$ and clock pulse stealing                                        |     |

|           | rate for chip 1. The circuit is aged by working for 100ks (~28                                                                |     |

|           | hours) at $V_{DD} = 1.2V$ and $130^{\circ}C$ temperature                                                                      | 102 |

"Shallow men believe in luck or in circumstance. Strong men believe in cause and effect." — Ralph Waldo Emerson, The Conduct of Life, 1980

# INTRODUCTION

Electronic systems are so widespread that it is impossible to find a piece of equipment that is not produced with them or does not contain them. Most of the electronic systems nowadays use semiconductor components. The advances in semiconductor technology have certainly been one of the key elements in making Apple, Alphabet (the parent company of Google), and Microsoft the top three largest companies of America as measured by market capitalization today [3]. Fig. 1.1 shows the largest firms of America over the past century. In 1917, more than 40% of America's largest companies (ranked by assets), were oil, steel or mining-related companies [1]. The invention of the transistor, as an alternative for the vacuum tubes, was announced on July 1, 1948, on New York Times, reported as "a device called a transistor, which has several applications in radio where a vacuum tube ordinarily is employed" [4]. In 1964, IBM introduced the industry's first high-volume, automatic, micro-miniature production of semiconductor circuits (Solid Logic Technology) [5]. Three years later, the most valuable company in America was IBM. Although IBM was the only technology company in that time, the technology firm was the second largest firm in America in 1967, as shown in Fig. 1.1. On July 18, 1968, Robert Noyce and Gordon Moore founded Intel, and three years later, Intel created the world's first commercially available microprocessor chip (Intel 4004) [6]. This microprocessor was built in  $10\mu m$  semiconductor process technology and included 2300 transistors [7]. The semiconductor industry continued to advance with exponential growth in the number of transistors that are integrable into a circuit. This exponential growth has been asserted by the well-known Moore's law which states that in a dense Integrated Circuit (IC), the number of transistors doubles about every 18 months at the same cost. In practice, it meant that the number of calculations per second per \$1 raised from 728.6 in 1973 to 133300 in 1998 [8]. In 2017, Qualcomm introduced the world's first 10nm server processor (Centriq 2400) which has ~7.8 million times more transistors inside compared to Intel 4004 [9]. As shown in Fig. 1.1, in 2017 America's largest firm by sector is technology. Today, with adjusting for inflation, Apple is worth more than twice what IBM was worth fifty years ago [1].

Figure 1.1: America's largest firms by sector in 1917, 1967, and 2017 [1].

The human's life has mainly been affected by industrialization, and the development of automation is inherent to industrialization because industrialization is defined to be the replacement of human or animal power by mechanical power [10]. A control system, as a necessary element of an automated system, is nowadays based on digital computers to perform the control calculations and transmit the proper commands [11]. Semiconductor technology scaling has been affecting human's life by making the computations faster, more power efficient, and cheaper [12]. However, technology scaling faces many challenges, including reliability [13].

The reliability of a system is connected with its failure rate [14]. The bathtub curves that are shown in Fig. 1.2 illustrate the effect of technology scaling on the failure rate of ICs. The bathtub curve is, in fact, the composition of three curves: early failures, constant failures, and wear-out failures. Depending on the dominance of each failure rate curve, the lifetime of the circuit is divided into three phases: Burn-in phase, normal life, and wear-out phase. The failure rate is high in the burn-in phase, mainly because of manufacturing defects, process variations, and design mistakes [14] [15]. The increased integration of transistors with technology scaling raises the rate of manufacturing defects, increases the spread in parameters of transistors and interconnects, and makes design more complicated [12]. During the normal life phase, the failure rate remains constant. In this phase, failures typically show themselves as temporary malfunctioning that happens randomly [14]. With technology scaling, the rate of these failures during the normal life period increases [12]. In the final phase of the lifetime, the failure rate increases due to silicon aging effects which cause permanent malfunctioning [14]. Silicon aging effects have become more pronounced in the scaled technology nodes [14]. These reliability issues have become critical considering the use of electronic systems in safety-critical applications.

Safety-critical systems are the systems which their failure causes injury or death, e.g., medical, automotive, or aviation systems. The use of electronic systems in safety-

Figure 1.2: The effect of technology scaling on the failure rate bathtub curve [2].

critical applications has become more popular over the years as shown by the following examples. A variety of parameters are regulated and monitored by electronic systems in a heart-lung machine to perform the oxygenation and pumping functions properly [16]. The modern radiation therapy machines rely on electronic systems to design patient-specific parameters to collimate and direct radiation beams for treating localized cancer, considering that excessive radiation is life-threatening [17]. In a modern passenger car, *Advanced Driver Assistance Systems (ADAS)* take care of some safety-related features such as adaptive cruise control, lane change assistance, and collision avoidance [18]. Without the *Fly-By-Wire (FBW)* system, many modern airplanes would not be able to fly. FBW replaces the traditional flight control interface, which is mechanical, with the electronic interface to reduce mechanical complexity and saving weight [19]. These examples not only show the importance of reliability in electronic systems but also they imply the importance of having a mechanism that can report the reliability status of the system while it is working.

Considering the importance of reliability in electronic systems (especially for safetycritical applications) this thesis is about finding an efficient way to make systems aware of their reliability. In what follows, the reliability issues of digital ICs are briefly reviewed, and timing unreliability is explained. Then, we state the problem that this thesis addresses. The requirements of the solution to this problem are explained next. The state of the art solutions are then surveyed. Then, the contributions of this thesis are clearly explained. And finally, this chapter is concluded by outlining the rest of the chapters of this thesis.

# 1.1 RELIABILITY OF DIGITAL ICS

Digital circuits are essential components of electronic systems. They allow us to implement algorithmic solutions, such as signal processing, communication, and control algorithms. Digital circuits take more advantage of technology scaling compared to their analog and RF counterparts [20], and reliability is the main issue that they face in the advanced process nodes. In this section, the critical reliability concepts that are used in this thesis are defined first. Then the sources of reliability issues for digital circuits are investigated. Finally, timing reliability as one of the primary requirement in digital circuits is explained.

# 1.1.1 Definitions

To define the terms more clearly, an example which implements the following function is considered

$$Y = a \times X + b, \tag{1.1}$$

where X and Y are input and output, respectively, while *a* and *b* are constants. The system is therefore made up of multiplication by constant *a* and addition to constant *b*. A **physical source** is the natural source of a reliability problem, i.e., it is the root cause of the problem. Due to this effect, a **fault** may appear in the system as a "weakness, blemish or shortcoming of a particular hardware component or unit" [21]. In the example system, a fault means malfunctioning of the adder or multiplier or changing the constants *a* and *b*. A fault can manifest itself in the system as an **error**, which is a deviation from the correctness of information inside the system [21]. In the example system, if a fault changes *a*, and the rest of the system is not faulty, the error does not happen as long as X = 0, while for other inputs, the fault manifests in the system as an error. Finally, a system **failure** occurs if it does not implement the intended function as a result of an error. In the example system, any deviation from the intended output according to (1.1) is considered as a failure for the system. Consequently, there is a cause-and-effect relationship between the physical source, fault, error, and failure.

**Reliability** is one of the most straightforward terms in the field with a quantitative definition. The reliability R(t) is defined for a system as the probability of its correct operation during the time interval [0, t] assuming that the system is operating correctly at time 0 [14]. In electronic systems, reliability is often modelled as a function of failure rate  $\lambda$  (shown in Fig.1.2) [14]

$$R(t) = e^{-\lambda t}.$$

(1.2)

According to (1.2), an electronic system is more reliable if the failure rate in that system is lower. The reliability status of a system can be tracked by sensing the physical sources of the problem, or by detecting faults or errors, or by observing system failure.

**Resilience** is defined as the "ability to deliver correct service adapting to disturbance, disruption, and change within specified time constraints" [21]. Therefore, a resilient system is inherently elastic and can adapt itself such that failure is avoided.

Figure 1.3: Cause-and-effect chain of timing unreliability.

# 1.1.2 Delay-Fault and Timing Unreliability

Digital circuits work based on logical operations which must be performed with appropriate timings. The logical operations are performed through logical gates that are based on compositions of transistors. The delays of logical gates and the wires which connect them are analyzed with design tools, and the selection of circuit structure and gates is made based on the specified design constraints. The design style of digital circuits is predominantly synchronous. A synchronous design is based on logical gates, memory elements, and a clock signal that regulates the timing in the circuit. The data which propagates inside a digital circuit can become erroneous if the circuit delays change such that the timing regulation which is imposed by the clock signal is violated, i.e., a timing error happens. If the timing error changes the functionality of the circuit, the circuit fails to perform its intended function. Therefore, it is essential to make sure that the circuit timing is reliable. Traditionally, the circuits are over-designed to make sure that their timings are reliable. This over-design approach is based on pessimistic timing characteristics at the design time.

The cause-and-effect chain of timing unreliability is shown in Fig. 1.3. Process variations, voltage drop, and temperature variations can be the physical sources of delay degradation in circuit components. Furthermore, silicon aging effects can increase the delays of the circuit components over time. Delay degradation is the *fault* which causes timing *error* in digital circuits. If timing errors are not prevented, they may result in system *failure*. The cause-and-effect chain of timing unreliability guides us towards techniques to increase the reliability of digital circuits and monitor their reliability (status) effectively.

#### 6 INTRODUCTION

# 1.1.3 Physical Sources of Timing Unreliability

The main physical sources that cause timing unreliability problems for the timing of digital circuits are variability and silicon aging effects. In this section, these effects are briefly reviewed.

The sources of variability are process and environmental variations [12, 22]. **Process variations** are due to the manufacturing process, while **environmental variations** affect the circuit when it is operating [22]. Variability causes deviations in the characteristics of circuit components. Extreme conditions are assumed at the design time to have a circuit which is reliable even in the presence of these effects. Alternatively, variability effects are modeled more precisely with a statistical approach to reduce the inherent pessimism of extreme condition assumption [22]. The environmental variations include temperature and supply voltage. The design should ideally work at the designed voltage, but due to effects like tolerance of voltage regulators, IR drops, or noise, the operating voltage can change. Similarly, the operating temperature of the circuit can change due to its environmental temperature or its own activity. The variations of temperature and supply voltage affect the characteristics of the circuit components. Technology scaling magnifies the sensitivity of circuit components to the environmental variations [23].

The effects of process variations are divided into global and local factors. Global process variations affect the parameters of all components of a die in the same way, while the effects of local process variations vary across the components of the same die. In [15], the global and local variability effects are characterized by inverter-based Ring Oscillators (RO) in different technology nodes. The results of their experiments are plotted in Fig. 1.4-(a) for 7-stage inverter RO and 29-stage inverter RO. As can be observed, global variations had a decreasing trend until 65nm while, and it increased again in the 40nm process node. On the other hand, the effect of local variations has been monotonically increasing with technology scaling trend. Traditional sources of process variations, such as mask offsets, mainly cause the global variation effects [24] while entering into atomic sizes with technology scaling magnifies the local variations. In Fig. 1.4-(b), the primary sources of local process variations in the smaller technology nodes are shown. The first effect is called Line Edge Roughness (LER), and it explains the fluctuations in lines due to the lithography limitations in the fabrication process. The other effect is called Random Dopant Fluctuations (RDF) which is about the fluctuations in the number of dopant atoms (which is a discrete number) inside the channel of transistors. Shrinking the sizes with technology scaling increases the relative effect of these fluctuations on the parameters of circuit components [24] [15].

Silicon aging effects are temporal reliability issues, i.e., they cause change in the characteristics of circuit components over its lifetime. The extent of these effects depends on the stress factors (i.e., working conditions of the circuits) and time. Some silicon aging effects manifest themselves by changing the performance parameters of the circuit (e.g., power or delays) gradually, while others lead to abrupt malfunctioning. Technology scal-

Figure 1.4: Variation effects. (a) The effect of process variations on inverter-based ROs with 7 and 29 stages in different technology nodes. (b) Cross-section of a transistor illustrating the roughness in the channel edges and the randomly placed dopant atoms inside channel.

ing has increased the effects of silicon aging [15, 24, 25]. The most severe silicon aging effects in sub-90nm technologies are *Time-Dependent Dielectric Breakdown (TDDB)*, *Hot Carrier Injection (HCI), Bias Temperature Instability (BTI)*, and *Electromigration (EM)* [25]. TDDB, HCI, and BTI effects are sources of unreliability for transistors, while EM affects circuit wires. TDDB and EM cause circuit breakdown abruptly, while BTI and HCI affect circuit timing gradually [15].

# 1.2 **PROBLEM STATEMENT**

Reliability of electronic systems is getting harder due to the technology scaling trends and challenges. Furthermore, the growing use of electronic systems in safety-critical applications intensifies the necessity of reliability awareness in electronic systems. Digital ICs are the typical component of almost all electronic systems, and they take the most advantage of technology scaling. However, the physical sources of unreliability, such as silicon aging and variability, challenge their reliability. Timing is one of the main concerns for the reliability of digital circuits as correct timing is important for correct operation of the circuits. Monitoring the timing reliability of digital circuits is therefore essential. This thesis investigates techniques to realize an efficient and reliable chip health tracking technique. The problem statement for this work is, therefore: *How to monitor the timing reliability of a digital circuit provided that the solution must 1) be reliable considering variability effects, 2) be cost-efficient to preserve the benefits of technology scaling, and 3) predict failures to avoid them, required in safety-critical applications.*

#### 8 INTRODUCTION

#### 1.3 REQUIREMENTS

Based on the problem statement, the following requirements are set for the demanding chip health tracking solution.

# 1.3.1 Real-Time

Continuous tracking of chip health status is essential to minimize the risk of failure. In safety-critical applications, the system must be checked during its operation because any risk of failure must be minimized in these applications. Therefore being able to perform continuous chip health tracking during operation (i.e., being real-time) is another requirement for the demanding chip health tracking technique.

For real-time chip health tracking, the tracking mechanism must run in parallel to the main workload of the circuit, i.e., the technique is not allowed to stop the system. Furthermore, the technique must be predictive of system failure, rather than being a detective technique. Being predictive allows minimizing the probability of failure by having some time to avoid failure. On the other hand, the detection-based approach tries to compensate for the failure effects, which is expensive and unacceptable for safetycritical systems. Since circuits are typically over-designed to be reliable, if the technique can report the available margin, it can predict the future failures, i.e., if the margin is low (high), the chance of failure is high (low).

# 1.3.2 High Coverage

The demanding chip health tracking technique can be seen as a system itself. The expected functionality of the system is to report all faults in the monitored system. The health tracking system fails when it does not report a fault in the monitored system, while the fault exists in reality. Hence, a reliable chip health tracking system must have high enough coverage. The definition of coverage here is similar to the definition of test coverage for *Design for Test (DfT)* techniques. In DfT techniques, the probability of a chip with fault not passing the tests is (1-T) where T is the test coverage. Therefore, it is necessary for a demanding chip health tracking technique to observe faults in all critical components of the circuit without missing any of them.

# 1.3.3 Cost-Efficient

Technology scaling has enabled digital circuits to be faster, more power efficient, and smaller. Any solution for the reliability problem which is faced by technology scaling must be cost-efficient in terms of speed, power, and area overheads. Otherwise, the benefits of technology scaling can diminish substantially. Therefore, one of the requirements

for the demanding chip health tracking is being cost-efficient in terms of speed, power, and area overheads.

# 1.3.4 Integrable in Standard IC Design Flow

The proposed solution for chip health tracking must be able to be integrated into the standard IC design flow. For this purpose, the technique must be based on a solid understanding of circuit timing and reliability models. Furthermore, the technique must be developed based on the standard IC design flow and the capabilities of industrial IC design tools. Otherwise, the reliability and practical feasibility of the technique are not appealing.

# 1.4 STATE OF THE ART

In this section, the state of the art in monitoring the timing reliability of digital circuits is reviewed. Based on what which is sensed in the cause-and-effect chain of timing unreliability (see Fig. 1.3), the state of the art is classified as follows:

- Physical source sensing techniques: The techniques in this category sense the physical source of timing unreliability, i.e., process, voltage, and temperature variations, and aging effects.

- Delay-fault sensing techniques: The techniques in this category aim to sense deviations of delay characteristics in digital circuits.

- Timing error sensing techniques: The techniques in this category check if the data has become invalid due to timing error.

In Fig. 1.5, the categories of related works are illustrated. In what follows, the related works in each of these categories are reviewed and assessed based on the set of requirements that were discussed before.

# 1.4.1 Physical Source Sensing Techniques

The effect of process variations on circuit performance is traditionally captured with worst-case assumptions for delays, i.e., adding timing margin. However, considering the worst-case delays imposes design costs in terms of power and area to meet a target speed for the circuit. The effects of process variations on the circuit performance are captured by employing either RO circuits [26, 27] or sensing the parameters of transistors such as threshold voltage [28–31]. Adding timing margins has also been the traditional way to address supply voltage variations. Supply voltage sensors are employed to reduce the cost of traditional over-design approach. In [32], the supply voltage sensors are categorized into three groups: Based on comparison to an external reference [33], over/under-shoot-detection-based [34], and Delay-based [35]. Furthermore, novel techniques like [36] predict dynamic delay variation due to the voltage drop caused by work-

Figure 1.5: The categorization of state of the art works in timing unreliability monitoring.

load variations with machine learning models. Due to the considerable effect of temperature variation on the circuit parameters, and the importance of temperature for circuit reliability, design of temperature sensors with high sensitivity has been extensively researched. Similar to process variation sensors, the existing temperature sensors are RO based (see, e.g. [37–39], or based on sensing the transistor parameters such as drain current (see, e.g. [40–42]. The cause of silicon aging effects is some specific physical stress on the transistors, e.g., temperature and voltage. Techniques that sense the silicon aging effects on circuit timing are either based on sensing the stress factors [43–46] or the extent of which the parameters of a transistor [47] (or the frequency of a RO [48]) under stress is degraded.

The techniques which are based on sensing the physical source of timing unreliability use sensors which are smaller than the main circuit. Therefore, the area, speed and power cost of these techniques are modest. Furthermore, since these techniques do not intrude the main design, their functionality does not require stopping the main circuit, and they can perform real-time chip health tracking in parallel to the main workload. Since these techniques are based on sensing the cause of timing unreliability, they are inherently predictive. Furthermore, the sensors can be designed to be more pessimistic and report the problem before the main circuit fails. Integration of the sensors in the standard IC design flow is not challenging as they can be considered like any other standard macro which is instantiated and physically placed and routed inside the design. However, the coverage of physical source sensors is minimal because they are not truly part of the main circuit and have limited accuracy in sensing the actual timing degradation of circuit components.

## 1.4.2 Delay-Fault Sensing Techniques

Any deviations from operational delay values of circuit components must be sensed to detect delay-faults in a circuit. There are three approaches to sense delay-faults: replica-based, delay testing, and slack monitoring.

In the replica-based techniques (see, e.g. [49–51], the critical timing components of the circuit are replicated, and their delays are measured. The main challenge in these works is the proper selection of critical components at the design time [52]. That is because replicating too many components of the circuit can annul the main advantage of this approach which is being low-cost in terms of power, area, and speed. Similar to physical source sensing techniques, the replica-based techniques can run in parallel to the main design, but they are less predictive than those techniques. Integrating the replica-based techniques is challenging because the timing-critical components of the circuit are identified at the very late design stages which means that the sensing circuitry should be added to the design when the design is almost finalized. This approach can add too much engineering effort and limit the accuracy of the technique. Finally, although the correlation between the delay defect in the main circuit and the sensed delay defect with the replicated circuit increases with this approach, still the number of replicated components are limited and the main components are not directly monitored with this approach. Therefore, the coverage of these techniques is limited.

DfT techniques add hardware to the main design and allow testing the IC for manufacturing faults. The use of DfT hardware to detect delay-faults is a standard technique [53]. Testing is performed by applying some test data to specific internal nodes of digital circuits, running the circuit to change the internal node data, and collecting the new internal data (test results) to compare them with a golden reference. Built-In-Self-Test (BIST) hardware is added to the main circuit to apply the test data and compare the test result in the field. Use of BIST for delay testing has been considered in the literature [54-62]. However, the hardware overhead of this approach is considerable. Furthermore, testing the circuit for delay-faults requires stopping the main functionality and applying test vectors and collecting the test results afterward. Since with this approach delay-faults are sensed, if some pessimism is added to the test [61] the test result can be predictive of the problem. Delay testing uses the mature DfT insertion flow which is integrated into standard IC design flow. The additional hardware which is specific for delay testing (mainly to manipulate the clock signal) is also nowadays added to the design in a standard approach using commercial IC design tools. However, the main challenge for on-line delay testing is the coverage. Since delay testing relies on activating the delayfaults by applying the test vectors, the coverage of the approach depends on the testing data. Most of the research efforts in this field have been dedicated to solve this issue.

Slack monitoring is another approach for delay-fault sensing. In the digital circuits, the clock signal determines the times at which the data is captured. If the delays increase in the system, the proper data is not captured, and a timing error happens. Slack is defined as the difference between the latest time that the data that should be captured arrives and the capturing moment which is determined by the clock signal. In practice, due to the worst-case assumption during design time, the slack value is nonzero (which indicated as the design margin). The slack monitoring techniques measure the slack value and report it as an indication of circuit delays. If the slack is smaller than a specific value, a delay-fault has occurred. The slack monitoring techniques are either based on canary flip-flops [63] or time-to-digital converters [62]. Both approaches add additional hardware components that capture the data earlier than the clock capturing moment. If the earlier captured data is different from the main captured data, it is considered as a warning signal that warns tight slack in the design (i.e., a delayfault). Although slack monitoring techniques can directly sense the delay-faults of a critical component in the circuit, since during optimizations with circuit design tools a large number of circuit components become timing critical [52], the cost of slack monitoring techniques is too high. Slack monitoring techniques can run in parallel to the main workload of the design without requiring to stop the main functionality. Furthermore, these techniques detect delay-fault which makes them more predictive compared to timing error detection techniques. The challenge for integration of these techniques in the standard IC design flow is identifying the critical components which should be monitored. Finally, the coverage of these techniques relies on activation of delay-faults during normal operation of the circuit. Since not all delay-faults are activated during the normal operation of the circuit, the coverage of these techniques is limited.

# 1.4.3 Timing Error Sensing Techniques

A timing error occurs when the data inside the circuit becomes invalid due to delayfaults. Generally, error detection techniques are based on some redundancy, i.e., hardware, information, ..., is replicated and the corresponding data from the primary and redundant counterpart(s) are compared to detect error occurrence [64]. The standard techniques in this category are *Double Modular Redundancy (DMR)* and *Triple Modular Redundancy (TMR)* techniques. These techniques can be employed with different design granularities (e.g., circuit components or systems-level). Using redundancy at the system-level suffers from common cause failure problems for aging [65]. In [66] redundancy was introduced to the sequential components of digital circuits (i.e., flip-flops) for the first time to achieve soft error resilience. The idea was later extended in [67], known as Razor flip-flops. Razor flip-flops detect timing error by sampling the data multiple times and comparing the results to detect a timing error. Later, the idea of Razor

| Technique        | cost | real-time |            | Integrability | coverage |          |

|------------------|------|-----------|------------|---------------|----------|----------|

| rechnique        | cost | parallel  | predictive | integrability | in-situ  | critical |

|                  |      | paraller  | predictive |               | iii-situ | elements |

| physical source  | low  | yes       | yes        | good          | no       | none     |

| replica-based    | low  | yes       | yes        | moderate      | no       | low      |

| delay testing    | high | no        | yes        | good          | yes      | low      |

| slack monitoring | high | yes       | yes        | poor          | yes      | low      |

| error detection  | high | yes       | no         | moderate      | yes      | high     |

Table 1.1: Assessment of the state-of-the-art works in timing unreliability monitoring based on the set of requirements for the demanding chip health tracking system.

flip-flops was investigated extensively, and different flavors of the idea were introduced in the literature [68–73]. These techniques are generally known as *Error Detection Sequential (EDS)*. The main advantage of EDS techniques is that they sit at every flip-flop and in this way they sense if any data has become invalid due to timing degradation. Note that error detection with this approach still relies on the error activation by the workload of the design. Furthermore, they can run in parallel to the main workload without requiring to stop the main functionality. However, the cost of this approach is too high due to the significant design overhead, and they perform detection instead of a prediction of timing error. Integration of these techniques into the standard IC design flow is done by replacing the regular flip-flops with the EDS counterparts and setting appropriate timing constraints. Therefore, these techniques can be integrated into the standard IC design flow.

# 1.4.4 Summary of Related Work

In Table 1.1, assessment of the state of the art is summarized. Increasing the coverage of physical source based and replica-based techniques requires adding too many sensing which annuls the low-cost benefits of those techniques. Delay testing techniques inherently cannot be real-time because applying the test data and collecting the test results requires stopping the circuit and its main functionality. Similarly, error detection techniques cannot be real-time techniques because they are naturally detect timing errors instead of predicting them. On the other hand, slack monitoring techniques can be improved and could then fulfill the requirements. The focus of this thesis is investigating the slack monitoring based techniques and improving their cost-efficiency, integrate them into the standard IC design flow, and improve their coverage.

Figure 1.6: Thesis contributions.

# 1.5 APPROACH AND CONTRIBUTIONS

Based on the set of requirements that were discussed in Section 1.3, and the state of the art works, the main goal of this thesis is to develop a reliable, low-cost, and predictive technique for monitoring timing reliability of digital circuits based on in-situ delay monitoring. Following this goal, some contributions are made in this thesis. These contributions are shown in Fig. 1.6 and briefly explained in what follows.

# 1.5.1 More Accurate Timing Model

Accurate modeling of circuit timing and its unreliability effects are essential to develop a well-founded chip health tracking technique. In Chapter 2 of this thesis, the concepts related to the timing of the digital circuit is reviewed, and timing unreliability is modeled. Besides, a novel timing model is proposed for sequential components of the digital circuit (i.e., flip-flops). The proposed model takes the inter-dependency of timing constraints into account with higher accuracy and less characterization effort. The proposed model is integrated into the timing analysis flow. Consequently, the design efficiency is improved in terms of power, area, and speed, and timing sign-off is moderated by reducing pessimism in timing analysis. Moreover, a new procedure is proposed in Chapter 2 to model the timing unreliability in standard IC design and timing analysis tools.

# 1.5.2 Effective In-Situ Delay Monitoring