# CHAPTER 5

# NETWORK AND TRANSPORT LAYERS IN NETWORKS ON CHIP\*

The main goal of the network and transport layers is to support the endto-end communication between the modules at the specified *quality of service* (QoS) using a power- and resource-efficient sharing of the interconnect resources. This seemingly simple goal forces the designer to address all classical (and some new) network layer issues in the context of an individual chip design.

In order to define the end-to-end QoS, we need to define the on-chip communication requirements in terms of the module-to-module traffic types, rates, statistical behavior, and predictability. For each such end-to-end *flow* we also need to define the service it receives such as loss and delay. We also need to define the interrelation between these flows, such as priorities, and actions that should be taken when communication resources are scarce. Finally, we need to decide on the appropriate network architecture that supports the above QoS requirements. For this the following *network on chip* (NoC) characteristics must be defined: switching technique, NoC topology, addressing and routing scheme, and end-to-end congestion and flow control schemes.

First, the appropriate data switching mechanism (e.g., circuit switching, packet switching, etc.) needs to be selected for the multiplexing of multiple flows from different sources and different requirements in a single network. Then, the appropriate network topology needs to be selected and optimized to physically connect the different modules (including basic graph topology, links and router speeds, and specific layout issues). Addressing and routing schemes need to be devised in order to allow circuit or packets traversing the network to be routed to diverse destinations including possible multicast or broadcast of information. Names meaningful to applications (such as memory and I/O addresses) need to be translated into routing-efficient labels. Since the proper delivery of certain types of traffic (or signals) on the chip is crucial for performance and is categorized in different ways, the concurrent support of multiple QoS

<sup>\*</sup> This chapter was provided by Israel Cidon, of Technion, Israel and by Kees Goossens, of Philips Research, The Netherlands

requirements is essential. Since modules perform a variety of information exchanges, there is a need for end-to-end mechanisms to guarantee in order and assure delivery, end-to-end connection and flow control for rate matching and receiver buffer management and resource access control for multiple resource access resolution. In order to accommodate excessive traffic conditions and to quantify the behavior of the network under extreme conditions, NoC should also support network-level congestion control. One also needs to address reliability in the face of communication soft errors that may corrupt transmitted data.

# 5.1 NETWORK AND TRANSPORT LAYERS IN NoCs

The network layer deals with the QoS, switching technique, topology, and addressing and routing schemes. The transport layers address the congestion and flow control issues. However, we will not make the distinction in the remainder of this chapter.

Since similar network and transport layer problems have been extensively studied in the networking and system interconnect realm, one may be tempted to employ well-developed networking solutions in the NoC context. However, a direct adaptation of such network solutions to NoCs is impossible, due to the different communication and performance requirements, cost considerations, and architectural constraints [21].

First, the requirements are different. Unlike many off-chip networks, the NoC is at the heart of chips that support real-time operations and are embedded in critical systems from life-support gear to vehicular and aerospace equipment. Embedded systems also often deal with intrinsically real-time data, such as high-quality audio and video. Therefore, NoCs QoS requirements call for a high degree of predictability and robustness and cannot tolerate incidental glitches and anomalies [32]. As a specific example, network design must meet strict QoS requirements for certain types of traffic, such as interrupt signals or fetching real-time instructions and data from caches to *digital signal processors (DSPs)*. Such requirements may be specified in very strict terms, such as the number of clock cycles to accomplish a certain transaction.

Second, the cost considerations are different. The primary considerations in *very large-scale integration* (VLSI) are minimizing area and power dissipation. The area cost of an NoC is composed of routers and network interfaces (i.e., logic cost) and the cost of wires/links that interconnect them (area used by metal lines, spacing, shielding, repeaters, etc.). Similarly, power consumption can be separated to dynamic and static power consumed by the NoC logic (in routers and network interfaces) and links (in wires and repeaters). In both cases, both temporal power to reduce heat dissipation, and total energy consumption for saving battery power for nomadic systems [12] are to be minimized. Moreover, since an NoC

connects modules or relatively small subsystems, these area and power costs should be kept much lower compared to networks that connect large systems.

Third, there are also many architectural constraints and freedoms unique to the NoC environment. For example, on-chip network topologies are quite restricted – they are planar, often organized as (full or partial) grids, and do not need to support the dynamic addition or removal of components. A new important dimension of freedom in NoC is the ability to alter the physical layout of the network routers and links along with the chip module placements, enabling the designer to optimize the NoC geography according to traffic and layout constraints [13, 78, 80].

Furthermore, each NoC is synthesized anew for each design [43, 62], eliminating the need for standardization of network protocols. That is, protocols and architectures employed in a new chip design do not have to be compatible with those used in previous designs. Consequently, NoCs do not possess the rigid standardization constraints of traditional networks. Except for retaining module reuse compatibility, NoCs can be customized to their specific chip environment and need not assume backward, upward, and different vendor compatibility as well as regulatory constraints. In that sense the NoC environment is much more open to multiple choice and architectural innovations. Nevertheless, the use of standard network interfaces, such as *Open Core Protocol* (OCP) [86] and *Advanced extensible Interface* (AXI) [2] is important, in order to allow the reuse of modules, across chip designs.

## 5.1.1 Classifying NoC Models

As mentioned in Chapter 1, Networks on chip can be classified into different families. We elaborate more on this concept here, and relate to a classification of chip designs based on Ref. [21] and on its impact on NoC design. *Systems on chip* (SoCs) span a vast spectrum of objectives and implementations.

On one extreme of the spectrum we identify the *application-specific* SoCs or ICs (ASICs), encompassing custom-made designs with a particular preknown application, for example, a multichannel 3G base-station, a video camera, or a set-top box. In such chips, the network usage is known *a priori* and can be classified prior to the NoC design time.

On the opposite side of the spectrum, general-purpose *chip multiprocessors (CMPs)*, capture general-purpose chip designs supporting parallel processing, where the chip and interconnect usage is unpredictable and only determined at run time. Here we can find general multi-core processors, parallel DSP arrays, etc.

In between these two extremes we can find designs whose traffic patterns can be partially predicted, or may have several distinct usage patterns. These systems are the outgrowth of *application-specific standard*

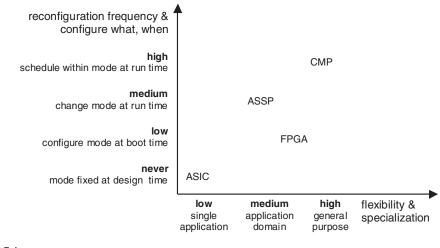

#### ■ FIGURE 5.1

An NoC classification.

*products* (ASSP); also called *application-specific instruction set processors* (ASIPs), which are processors whose architecture has been tuned to an application. SoCs may contain multiple processors and mix general-purpose and application-specific processors. In general, it is commonplace to refer to *platforms* as to multiprocessors dedicated to a family of applications.

The *field-programmable gate arrays (FPGAs)* define multipurpose chips that include generic hardware resources like logic arrays, flip-flops, RAM, processors, and special purpose *Internet Protocol* (IP) modules (Ethernet, USB, DSP) that can be *configured* using a programmable interconnect grid, into specific systems. The design of such systems leaves a large degree of freedom for the FPGA designer (programmer).

We illustrate the NoC design spectrum in Fig. 5.1.

#### ASIC

The distinguishing property of our ASIC NoC definition is the ability to predict the network usage patterns before the network is designed. Since a typical SoC has a specific functionality, this functionality can be simulated, and the inter-module communication patterns and requirements can be inferred at design time. Consequently, a specific NoC can be synthesized to satisfy these exact needs. Virtually all network parameters, including network layout, link capacity allocation, buffer sizes, packet headers, partial routing tables, and the number and requirements of service classes, can be custom synthesized to meet the particular SoCs requirements with no "open-ended" resources spent on "general-purpose" requirements. Specifically, most SoCs do not need to support all possible module-to-module

communication patterns as well as all possible QoS classes for all modules or SoC vicinities.

ASICs are optimized for the application, and hence will have the smallest area and use the least power. This comes at the cost of reduced flexibility. Related to this is the cost of designing an ASIC, which is incurred most often of all categories, namely for each application.

#### **ASSP** and platforms

A slightly more complex scenario is dealing with SoCs that are designed to support multiple applications, or that can take different chip "incarnations" at either production or power-up time. In such SoCs different modules and different software may be operating in each distinct SoC incarnation. A major design objective is to build a single SoC for a broad range of related applications [99]. In such a case the NoC is designed to support all possible applications. However, for each specific incarnation the NoC can be configured to operate at minimum power consumption. Therefore, non-required elements can be turned off and dynamic voltage and frequency scaling (DVS/DFS) techniques can be used to tune the NoC for an optimal performance versus power trade off [79].

ASSPs/platforms are tailored to an application domain (e.g., high-end set-top boxes), rather than to a particular application. They are less area and power efficient than an ASIC for each application. However, the increased flexibility is rewarded by reuse of the chip for multiple applications. As a result, the cost of designing the ASSP/platforms is paid only once per application domain.

#### FPGAs

An FPGAs NoC is designed in two phases: (i) the *layout phase*, which occurs when the FPGA chip is designed and (ii) the *configuration phase*, occurring when a system design is programmed into the FPGA. The design made in the former should be flexible enough so as to allow for a large variety of configurations during the latter. Unlike in the ASIC model, little is known about traffic patterns when the network is laid out, and hence, custom optimizations are impossible. In the configuration phase the traffic patterns become available, but the physical wires and network resources are already fixed in place.

The NoC infrastructure can be designed into the fixed FPGA fabric during the layout phase. But it can also be programmed, just like any other functionality, during the configuration phase. In the former case, the communication patterns of the application to be programmed in the FPGA are not yet known, and the NoC must therefore be a general one (like for CMPs, described below). But the implementation of this NoC can be highly optimized, for example using custom layout. The reverse holds for the latter, where the application and its communication patterns are known, and an NoC optimized for the application can be programmed in the FPGA. The

NoC implementation will therefore use the generic FPGA infrastructure (look-up tables, switch boxes, etc.), just like any other module functionality. As a result, the NoC implementation will be much less optimized. Of course, a mixture of these two models is also possible. For example, an NoC backbone (routers and network interface kernels) is designed in the FPGA, which is augmented with network interface shells [91] during configuration.

FPGAs are optimized for hardware-programmable flexibility. Hence, they are very area and power inefficient compared to an ASIC for each application. However, their computational efficiency is good compared to ASICs and ASSPs. Because the FPGA is designed once and then programmed, it is able to run all applications. The design cost of an FPGA is amortized over a larger number of applications than ASICs and ASSPs.

#### **CMPs**

In a general-purpose CMP, the traffic pattern is completely unpredictable until run-time and even during different phases of the same program because of very different program behaviors for different external inputs (e.g., dynamic games, simulations, etc.). In this regard, many of the challenges of CMP NoC design resemble those we normally see in traditional networks, for example, static versus dynamic routing, congestion control, connection rate fairness, etc. Unfortunately, traditional mechanisms for dealing with these issues may be prohibitively expensive to implement in silicon. On the other hand, the relatively small dimension of the complete network, combined with the fact that the entire chip is often controlled by a single operating system, may make the problems amenable to centralized solutions.

CMPs are optimized for software-programmable flexibility. Hence, they are very area and power inefficient compared to an ASIC or ASSP for each application. The CMP is designed once (in theory) and is able to run all applications. Of the four categories, the design cost of a CMP is amortized over the largest number of applications.

In the sequel we present the different aspects of the network layer architectures and their design choices: the QoS and traffic requirement characteristics, the switching paradigm, NoC topologies, the addressing and routing mechanisms, handling congestion control, and end-to-end transport layer issues.

# 5.2 NoC QoS

There are many important metrics for NoCs. In this chapter, we devote particular attention to QoS, because this requirement has a direct impact

5.2 NoC QoS

on switching and routing. QoS is a common networking term that applies to the specification of network services that are required and/or provided for certain *traffic classes* (i.e., traffic offered to the NoC by modules). QoS specification can be expressed by performance metrics like loss, rate, delay, delay variation (jitter), etc. and can be categorized by absolute (worst case) bounds, average values, percentiles etc. [4]. For example, an Internet packet-based voice traffic may require a throughput of 64 Kbps, less than 1% average packet loss and a packet one way delay bound below 150 ms. QoS definitions can also apply to different service granularities. In addition to the QoS specification of voice packets, the whole voice call can require a limit on its call blocking probability (failure rate) or a specification of the call establishment times.

If certain traffic classes require an assured (guaranteed) QoS specification, there is an inherent limit to the amount of traffic that can be allocated to such a class. In other words, when there are more potential users than the network can support, some of them will be refused access to the network. Therefore, in our voice examples, the network is designed for a limited voice offered load. In case there is a risk that the user load may overpass this limit, special provisions need to be taken in order to block the excess offered load (e.g., a busy signal for telephone users).

The NoC applications (such as DSP, consumer electronics, etc.), usually stress the need for stringent bandwidth and/or latency requirements. NoC traffic can consist of urgent tasks such as code fetch following a cache miss, CMP synchronization signals or periodic refreshed data that need a guaranteed latency. Other urgent tasks may require similar latency with a high probability. Yet streaming traffic, such as audio and video, has strict bandwidth and jitter requirements, but tolerates long latencies [46]. On the other hand, certain traffic classes may not be planned for a guaranteed service (as they may produce an unspecified amount of traffic) but may require a graceful degradation of service as well as a fair allocation of the available resources as offered load increases.

The mixture of different service classes in the same network poses a special challenge to the NoC designer as each class may affect the performance of other classes. In other words, QoS also specifies how to allocate network resources at times of conflict over the network resources. Therefore, QoS mechanisms usually combine mechanisms for traffic discrimination (such as applying delay or loss priorities [18]), mechanisms for traffic separation (such as fair queueing mechanisms [48]), and mechanisms for traffic policing (enforcing limitations of traffic generation at the source modules). We return to some of these issues in Sections 5.4, Switching techniques and 5.7, Congestion control and flow control.

While the available QoS depends on the overall NoC architectural components such as topology, link and router capacities, routing algorithms, and congestion control mechanisms, it is common to separate the issue of QoS from other network issues. The rationale is the following: given

a complete network architecture we would like to be able to serve multiple traffic classes over the same network each with a different QoS specification. To achieve this, we need special mechanisms that isolate and differentiate these traffic classes within the network. These specific mechanisms are described in this section.

#### 5.2.1 Traffic Classes and Service Classes

The definition of traffic classes is an open-ended task and NoC designers can specify and support any number of classes. However, practice has shown that the specification, management and implementation of a large number of classes are complex and ambiguous task. First, it is hard to predict ahead of time all the future possible NoC usages. Here we should differentiate between different NoCs in our design spectrum where ASIC and ASSP NoCs are much more predictable than CMP NoCs. Second, the exact interrelationships between the classes are hard to define. Finally, the mechanisms that allocate the exact performance to each class in a multiple performance metrics domain (loss, rate, delay, jitter, etc.) are complex and costly.

#### Traffic classes and service classes in computer networks

Consequently, most off-chip network standards have aggregated the large number of possible traffic classes (traffic offered to the NoC by the modules) into a few predefined *service classes* (offered by the NoC to the modules). Let us illustrate the way the *asynchronous transfer mode* (ATM) and IP networking standards have classified the different traffic classes.

The ATM network defines five possible standard classes [74]:

- 1. *Constant bit rate (CBR)*: associated with traditional time division multiplexing (TDM) services where delay and loss are fixed and small.

- 2. *Variable bit rate real time (VBR-RT)*: associated with variable rate (usually compressed) real-time services that produce a predictable average rate and require low delay and jitter and can tolerate small loss.

- 3. *Variable bit rate non-real time (VBR-NRT)*: associated with less interactive real-time services such as streaming or high-priority data services.

- 4. *Available bit rate (ABR)*: includes most data services. The term available bit rate means that under bandwidth shortage conditions, the bandwidth allocated to this class should be allocated fairly among competing applications within this class.

5. *Best effort (BE)*: low-revenue and low-priority data that can serve as "bandwidth gap filler" such as file sharing or background synchronization traffic.

In a typical ATM implementation, the CBR and VBR service classes are accomplished via bandwidth reservation before use: a router priority mechanism among these classes and external user traffic policing guarantee no oversubscription. The ABR is accomplished using a network to user feedback control loop to assure a fair allocation of resources among all sources that share a congestion link. The BE is given the lowest priority and can take what is left. We discuss these issues for NoCs in the Section 5.4 on switching, and Section 5.7 on end-to-end control.

IP networks have two main QoS standards. IntServ [16] is a per (endto-end) flow QoS standard and therefore require a rather complex implementation in the Internet. DiffServ [82] defines the differentiated service field with six possible service classes which are similar to the ATM ideas.

#### Traffic classes and service classes in NoCs

While NoC traffic classes can be mapped to ATM, IntServ, or DiffServ service classes, the direction translation of general computer networks to NoCs is not appropriate, as described in the introduction. Moreover, the specific NoC service classes should be defined based on the vast experience in supporting ASIC and CMP communications over busses and dedicated interconnection infrastructures. Another key factor that separates NoC-based designs from a general network environment is the intrinsic characterization of on-chip communication. In addition, to general message-passing type communication, modules exchange low-level signals and distributed-shared-memory transactions that are typical to SoC flows. Examples are timing and synchronization signals, control words, cache invalidations, and interrupts that require an immediate and timecontrolled transfer. Memory transactions such as read/write (RD/WR), code fetch and pre-fetch, semaphore-based operation, and DMA transfer may vary in their timing priorities and urgency. Finally, I/O traffic and off-chip memory access needs to cross chip boundaries via drivers and external pin bottlenecks.

Each designer can identify service classes for a specific NoC implementation. We describe three NoC traffic and service classes in the remainder of this section:

Goossens et al. [46] characterize different traffic classes in ASIC and ASIP SoCs. The heterogeneity of processing modules results in a variety of traffic classes, based on data rate, latency, and jitter characteristics (see Table 5.1).

Control traffic originates from control tasks that are usually mapped on one or more processors, and which must obtain status

**TABLE 5.1** ■ A classification of traffic classes [46].

| Example                    | Data rate | Latency  | Jitter   |

|----------------------------|-----------|----------|----------|

| Control traffic            | Low       | Low      | Low      |

| Cache misses               | Medium    | Low      | Tolerant |

| Cache pre-fetch            | High      | Tolerant | Tolerant |

| Hard real-time video       | High      | Tolerant | Low      |

| Soft real-time video       | High      | Tolerant | Tolerant |

| Audio and MPEG2 bitstreams | Medium    | Tolerant | Low      |

| Graphics                   | Tolerant  | Tolerant | Tolerant |

information from modules and program them. It has a low data rate, but requires low latency to minimize the system response time, for example, when the application mode changes.

Multi-tasking processors, such as high-performance VLIW processors, do not have sufficient local memory to contain all instructions (code) and data of the multiple tasks. Instruction and data caches are therefore used to automatically swap in and swap out the appropriate instructions and data. This leads to medium (but instantaneously high) data rates, and requires low latency. On the other hand instructions are also speculatively pre-fetched ahead of time resulting in higher traffic that is both latency and jitter tolerant.

Dedicated video-processing modules usually operate on and generate streaming (sequential) traffic with high data rates. They are composed in deep chains without critical feedback loops, and their low-latency requirement can therefore be made less critical by using buffers to avoid underflow. The resulting traffic has a high data rate but is latency tolerant. Medium-data-rate latency-tolerant traffic is generated, for example, by audio and MPEG2-processing modules.

Jitter (latency variation) can be handled similarly, and we use the distinction between low-jitter (hard real time) and jitter-tolerant (soft real time) traffic. Modules with the latter traffic, such as the memory-based video scaler, have an average data-rate requirement but can be stopped when there is no data, and make up by processing at a higher rate later, or by averaging out data bursts. By contrast, low-jitter modules do not tolerate variations in data rates, because they cannot make up for any lost processing cycles. Examples are video-processing modules operating at actual video frequencies, where line and field blanking cannot be used as slack.

- Another rich example of a service classes set was given in Ref. [13] to illustrate a common NoC environment:

- Signaling covers urgent messages and very short packets that are given the highest priority in the network to assure shortest latency. This service level is suitable for interrupts and

control signals and alleviates the need for dedicating special, single-use wires for them. Some of the signals may also take the form of a complete transaction (such as semaphore operations).

- *Real-time* service level guarantees bandwidth and latency to real-time applications, such as streamed audio and video processing or the timely refresh of an LCD screen. While these operations need a guaranteed time for completion, the time limit itself may be quite large compared to other operations.

- *RD/WR* service level provides bus semantics and is hence designed to support short memory and register accesses. This class may be subdivided according to the urgency of the operation (fetching code, capturing resources). Extremely urgent R/W transactions may utilize the signaling service class.

- Block transfer service level is used for transfers of long messages and large blocks of data, such as cache refill and DMA transfers.

- Several NoC studies have observed the need to classify traffic and differentiate the service according to pre-specified service classes. The Æthereal [44] and Mango [8] architectures mainly address ASIC and ASSP SoCs for consumer electronics and have separated the services into two distinct classes: guaranteed throughput (GT) and BE. The GT class (similar to the above ATM CBR) accomplishes a TDM like service by limiting the GT traffic to a limited number of periodic flows and prioritizing the GT over the BE. With the right router architecture, this bounds the delay transfer through the network [61].

It should be emphasized that like other NoC design issues, each specific NoC implementation may define its unique set of service classes and also define how to map various traffic classes to service classes. Classifying traffic class may prove to be a challenging issue that involves knowledge of the specific modules' internals. For example, it may turn out that a seemingly single traffic class (memory read operation) needs to be split into several QoS subclasses. For example, fetching code (a memory read operation) to a processor module is sometimes much more urgent (an instruction fetch was missed in a local cache) and sometimes much less urgent (a pre-fetch operation with no current miss) than fetching data (another memory read operation) at the same processor. In such a case the module that originates the memory read instructions may map these similar operations to different classes of service, yet they look identical to an external observer who is not aware of the original cause of these transactions. Connection (identifiers) can be used to indicate to the NoC to which traffic class a transaction belongs [56, 92].

The SoC type impacts the traffic classes that may be expected, and hence the NoC service classes that the NoC must offer. ASICs, ASSPs, and FPGAs implement specific, hard real time, often relatively static applications known in advance [99]. Hence, we can expect service classes that are tailored for assured (guaranteed) real-time data streaming. CMPs, on the other hand, execute a variety of dynamic soft real-time applications that are unknown in advance, and BE service may be the dominant service class.

# 5.3 NoC TOPOLOGY

NoC architectures and topologies have been described in Chapter 2. In this section, we summarize for convenience the main characteristics of NoC topologies, and we relate them to cost metrics such as area, performance, and power consumption.

Network topology has been intensively studied in the context of highperformance networks [33] and parallel computers architectures [23]. Here, we introduce the concepts germane to NoCs, and refer to [23, 33] for more extensive classifications.

NoCs differ from general networks because they are realized on a plane, even though new technologies, like the emerging die-stacking and three-dimensional integration techniques may change this in the future. Moreover, links between routers can travel only in X or Y direction, in a limited number of planes (the number of metal layers of the IC process). As a result, many NoCs have topologies that can be easily mapped to a plane, such as low-dimensional (1–3) meshes and tori. We list here some important topologies for NoCs, and discuss area cost and performance for each group:

- *Crossbar*: When all routers are connected to all other routers, the NoC is fully connected. The result is single crossbar [67, 68]. It does not scale up to large number of network interfaces.

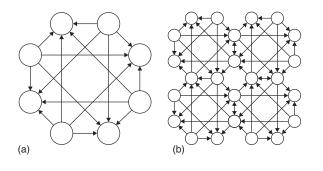

- *n-dimensional k-ary mesh* (or grid): The two-dimensional 2-ary mesh is a popular NoC topology because routers can be preplaced in layout, and because all links have the same (limited) length. The number of network interfaces per router is usually one, but can also be higher. Examples include QNoC [13] and Nostrum [75]. The area of meshes (the number of routers and network interfaces) grows linearly with the number of cores. Meshes have a relatively large average distance between network interfaces, affecting power dissipation negatively. Moreover, their limited bisection bandwidth reduces performance under high load. Care has to be taken to avoid accumulation of traffic in the center of the mesh (creating a *hot spot*) [83].

5.3 NoC Topology

*k-ary n-cube (torus)*: The *k*-ary 1-cube (one-dimensional torus or ring) is the simplest NoC, and is used in Proteo [93]. The area and power dissipation costs (related to the number of routers and network interfaces, and the average distance) of the ring grows linearly with the number of cores. Performance decreases as the size of the NoC grows because the bisection bandwidth is very limited.

The 3-ary 2-cube (two dimensional) torus adds wrap-around links to the two-dimensional mesh. To reduce the length of these links, the torus can be folded. Dally and Towles [30] use this topology. The area of tori is roughly the same as for meshes (some links are added), but the power dissipation and performance are better because the average distance is less than in meshes.

- *Express cube:* Meshes and tori can be extended with bypass links to increase the performance (bisection bandwidth and reduced average distance), for a higher area cost. The resulting express cubes [25] are essentially used in FPGAs.

- *d-dimensional k-ary (fat) trees*: These have *d* levels, in which each router has *k* children, network interfaces are attached only to the leaves. Examples are SPIN [50, 88]. The bisection bandwidth of tree is very low, due to concentration of all traffic at the root of the tree. To solve this problem the root can be duplicated. The resulting *fat trees* [69] (or folded butterfly) have a large bisection bandwidth (and hence performance), but associated high area cost. For larger number of nodes, the layout of the fat tree is more difficult, in comparison with meshes or tori.

- Irregular: NoCs are appropriate when the NoC can be optimized to a particular application domain or set of applications. Synthesizing application-specific NoCs in general at the desired costperformance point is a challenging problem. Examples of NoCs that allow irregular topologies are Xpipes [5] and Æthereal [44]. Optimized irregular NoCs can also be obtained by removing unnecessary routers and links from a regular NoC. For example, a mesh can optimized to a partial mesh [13], which has sufficient performance for the application at hand, but at lower cost.

#### NoC types and topologies

There is no strict correspondence between the different types of SoC (application specific, reconfigurable, or general purpose) and their topologies. However, we can discern some general trends.

ASIC and ASSP NoCs tend to be irregular (reduced meshes or completely optimized), because much is known of the application (domain) and NoCs can be highly tailored [99]. The area and power dissipation costs can be reduced, while performance is still guaranteed. For

example, the simple irregular tree topology is already used in commercial products.

FPGAs are composed of small-grained tightly coupled computation and storage units (look-up tables, RAMs, etc.). These units communicate mostly locally, and require high bandwidth and low latency for communication. As a result, express cubes (meshes with bypasses) are mostly used in FPGAs. The NoC is configured infrequently, and has high performance in the steady state.

NoCs for CMPs tend to consist of large-grained loosely coupled (usually homogeneous) computation subsystems (called tiles) [100, 104]. Tiles usually contain a local interconnect such as a bus or switch for frequent local communication, and use the NoC for less frequent global communication. As a result, two-dimensional meshes or tori (with limited bisection bandwidth) are the preferred NoC topology. Because applications are unknown at design time, NoCs are usually not statically configured but schedule traffic at run time.

# 5.4 SWITCHING TECHNIQUES

Once the topology of an NoC has been decided on, the switching technique, or how data flows through the routers, must be determined. This involved defining the granularity of data transfer, and the switching technique.

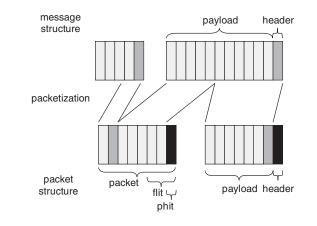

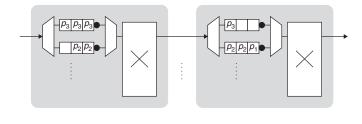

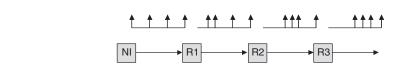

Data is transferred on a link, which has a fixed width, measured in bits. The unit of data transferred in a single cycle on a link is called the *phit* (physical unit). Two routers synchronize each data transfer, to ensure that buffers do not overflow, for example. Link-level flow control is used for this, and can be based on hand shaking or the use of credits [64]. The unit of synchronization is called a *flit* (flow control unit), and it is at least as large as a phit. Finally, multiple flits constitute a *packet*, several of which may make up *messages* that modules connected to the NoC send to each other. (Note that messages can be used for different NoC programming paradigms, including message passing and distributed-shared memory, cf. Chapter 7.) Fig. 5.2 shows this structure. To increase the packetization efficiency [42] message and packet boundaries do not need to be aligned, as shown.

Different NoCs use different phit, flit, packet, and message sizes. The phit and flit sizes reflect different design choices, such as link speed versus router arbitration speed [89]. For example, Æthereal uses phits of 32 bits, flits of 3 phits (or words), and packets and messages of unbounded length. Nostrum [75] uses phits of 128 bits, and flits equal to 1 phit. SPIN [50] uses phits and flits of 36 bits, and packets can be unbounded in length.

Phits are relevant for the link layer (Chapter 4), and will not be further discussed. The switching technique determines how flits and packets

#### 5.4 Switching Techniques

#### FIGURE 5.2

Phits, flits, packets, and messages.

are transported and stored by the routers, as described below. Chapter 7 further discusses messages. Note that the switching technique determines how data flows through the NoC, but not along which route. This is the subject of the next Section 5.5.

There are two basic modes of transporting flits: *circuit switching* and *packet switching*. Essentially, in circuit switching a circuit with a fixed physical path is set up between sender and receiver, and all the flits of the message are sent on this circuit. In contrast, in packet switching the packets constituting a message make their way independently from sender to receiver, perhaps along different routes, and with different delays. We discuss these techniques, and several variations, in more detail below.

To determine a switching technique for an NoC, a number of issues must be balanced, such as the granularity of the data to be sent, and the frequency with which it is sent; the cost and complexity of the router; the dynamism and number of concurrent flows to be supported; and the resulting performance (bandwidth, latency) of the NoC. Different types of NoC (ASIC, ASSP, FPGA, or CMP) often use different switching techniques, as we shall see. The switching technique strongly influences QoS, as mentioned in Section 5.2 and further elaborated in Section 5.7.3. In fact, to offer different QoS levels, NoCs can use multiple switching techniques at the same time [6, 44, 76].

#### 5.4.1 Circuit Switching

Messages from one module to another are sent in their entirety when using circuit switching. First, a physical path, that is, a series of links and routers, from sending to receiving module is determined and reserved for the circuit. Logically, the head flit of the message makes its way from

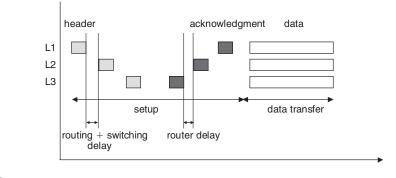

#### FIGURE 5.3

Circuit switching.

the sender to receiver, reserving links along the way. If it arrives at the receiver without conflicts (all links were available) an acknowledgment is sent back to the sender, who commences data transfer on its reception. If a link is reserved by another circuit, a negative acknowledgment is sent to the sender. Fig. 5.3 shows the set-up and use of a circuit over time; R1, R2, and R3 are routers along the path of the circuit. The shaded boxes show when the inter-router wires are occupied.

After transmission of the message, the circuit is torn down, as part of the tail flit. Pure circuit switching has not been used much in NoCs, and the principal examples are SOCBus [107, 108].

Circuit switching has a high initial latency due to the set-up phase that has to complete before data transmission starts. (Scouting routing [33] can reduce this time.) Data transmission is very efficient, however, because the full link bandwidth is available to the circuit, and results in minimal latency. Data does not have to be buffered in the routers (only pipelined perhaps), reducing the area of routers. However, circuit switching does not scale well as the diameter of the NoC grows [31, 107] because links are occupied also when data is not being transmitted (during the set-up and tear-down phases).

Circuit switching is appropriate when data is sent very often, or when the communication pattern between senders and receivers is relatively static. The circuit can be left in place in these cases. When the amount of data to be transmitted is large (making the set-up phase less relevant) circuit switching also works well. ASICs and ASSPs have relatively static communication patterns, and FPGAs also send data (bits or words) every cycle on the circuit. FPGAs (currently) exclusively use circuit switching, and ASIC and ASSP NoCs often do [44, 99, 108].

#### Virtual channels and virtual circuits

Circuit switching reserves physical links between routers. Multiple virtual links (more commonly called *virtual channels* [29]) can be multiplexed on a

5.4 Switching Techniques

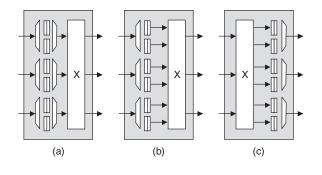

#### FIGURE 5.4

Virtual-circuit switching with multiple (2) virtual channels.

single physical link (channel). Virtual channels can be used to make circuit switching more flexible (see below), to increase performance by reducing blocking of links (described in Section 5.4.2), and to avoid deadlock (see Section 5.5).

Circuit switching reserves physical links between routers. *Virtual circuits* can be created by multiplexing circuits on links. The number of virtual channels that can be supported by a link depends on the number of buffers on the link. Two basic schemes have been used: a buffer per virtual circuit, or one buffer per link. Intermediate strategies are possible, but are more complex. We describe each scheme in turn, after which we discuss alternatives for circuit set-up and tear-down.

#### Virtual circuits with multiple buffers per link

A virtual circuit requires a buffer in each router it passes through. The spatial distribution of virtual circuits in the NoC therefore determines how many buffers are required in each router. This requirement can be used to determine the number of buffers for each router (virtual-circuit buffering). The number of buffers can then vary per router. Alternatively, the number of buffers per router can be given as constant and taken equal to the number of virtual channels (virtual-channel buffering). In this case, the number of virtual circuits using a given link is limited by the number of virtual channels on that link (and the routing algorithm, to avoid links of which all buffers are occupied). In both cases, virtual circuits are created by using virtual links, and it is only the determination of the number of the buffers in the routers that makes the difference. Fig. 5.4(a) shows the outline of a router with multiple buffers at the inputs of the switch. Fig. 5.4(b) shows how increasing the size of the switch from  $N \times N$  (where N is the router degree) to  $(V \times N) \times N$  (where V is the number of virtual channels) reduce the contention on the switch [44, 63]. Fig. 5.4(c) shows virtual-channel buffering with output queueing [8].

In any case, many systems contain hot spots, where many virtualcircuits converge, such as the external memory interface [46]. There will

Virtual circuit switching with a single buffer per link and TDM.

not be enough virtual channels for accommodate all flows. Virtual-circuit buffered router implementations become problematic either due to multiplexing the large number of small buffers, or due to the expensive (large) shared buffer implementations, such as SRAMs. Routers that implement virtual circuits with a single buffer per link obviously do not suffer from this problem, as described below.

The multiplexing of the individual virtual channels on a single link requires scheduling at each link/router, and results in an end-to-end schedule of the virtual circuits. Virtual circuits with input queuing are used by Refs [63, 108]. The scheduling of access to links and access to the (blocking) crossbar in the router interfere, making bandwidth and latency guarantees difficult to achieve. For this reason, the Mango NoC uses virtual-channel buffering implemented by output queuing with a non-blocking crossbar [8] (see Fig. 5.4(c)). This, together with an appropriate link scheduling scheme [9] enables it to guarantee bandwidth and latency on its virtual circuits.

#### *Virtual circuits with a single buffer per link*

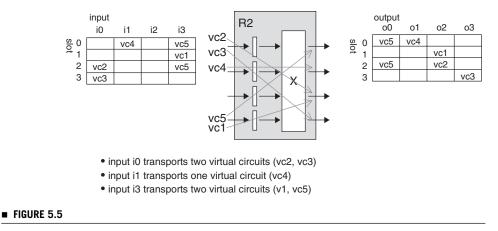

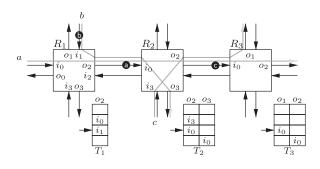

Circuits can also be time multiplexed with one buffer per link, that is, without requiring buffering per virtual circuit. Essentially this is achieved by statically scheduling (using TDM) the usage of all links in the NoC by all virtual circuits. Fig. 5.5 shows a  $4 \times 4$  router with four TDM slots. Each input has a one-flit buffer even though it can be used by up to four virtual circuits. The TDM tables show how virtual circuits are mapped from inputs to output in time. The example is described in more detail in Section 5.7.1 and is consistent with Fig. 5.20.

At the edge of the NoC, flits are injected by the network interfaces such that they never use the same link at the same time (see Fig. 5.20). As a result, link-level flow control and scheduling can be omitted, and only

one-flit buffer per link is necessary. This scheme assumes the propagation speed of individual flits through the NoC is fixed and known in advance. Flits wait in the network interfaces until they are injected in the NoC according to the TDM schedule. Note that network interfaces require some kind of end-to-end flow control for lossless operation, probably with virtual-circuit buffering (Section 5.7.2).

The TDM is used to globally schedule all flows, and hence end-to-end bandwidth and latency guarantees are easily given ([37]; Section 5.7.3).

The concept of globally scheduling all virtual circuits is used by NuMesh [96] (for parallel processing), Nostrum's looped containers [75], adaptive SoCs (aSoCs) global scheduling [65, 66], and Æthereal's contention-free routing [44, 90].

#### **Circuit management**

Set up and tear down of virtual circuits can take place as described at the start of this section. Options include static or dynamic reservations, back-tracking, and multicast. Care must be taken that deadlock does not occur during set up. This can be achieved by retracting a circuit [44, 107], or by dropping data [31]. Alternatively, a programming can be centralized in a single entity such as a programmable processor [44, 63, 108].

Set-up, (negative) acknowledgment, and tear-down can also be encoded as messages (usually just of one flit), like in the ATM [3] and pipelined circuit switching [33]. Set-up and tear-down messages program routers, using a message-based or memory-mapped protocol. Æthereal [44] and Mango [6] are examples of this approach. Control messages can use a different switching scheme (e.g., wormhole (WH) packet switching) and different QoS class (e.g., BE). Using messages allows circuit management to use the NoC itself, eliminating a separate control interconnect to configure the NoC [49, 108].

# 5.4.2 Packet Switching

In (virtual) circuit switching a complete (shared) path is reserved before data is sent. In contrast, in packet switching, no link reservations are made, and the packets constituting a message make their way independently from sender to receiver, perhaps along different routes, and with different delays. Omitting the set-up phase removes the start-up time (set-up until acknowledgment), but without link reservations, packets of different flows may attempt to use a link at the same time. This is called *contention*, and requires that all but one packet must wait until the link becomes available again. The start-up waiting time of circuit switching (followed by a fixed minimal latency in the routers) is replaced by a zero start-up time and a variable delay due to contention in the each router along the packet's path. For this reason, QoS guarantees are harder to deliver in packet-switched NoCs than in circuit-switched NoCs.

Store-and-forward switching.

The lack of resource reservations means that there is no limit to the number of flows (or connections) that a link or the NoC as a whole can support, in contrast to (virtual) circuit switching.

In packet switching, packets of different flows are automatically distributed over different links through the network (if dynamic routing is used), and interleaved on links. As a result, links can be dimensioned for (at least) the average amount of traffic. Virtual-channel or virtual-circuit buffering also interleave packets of different virtual circuits on a link, but all packets of a virtual circuit always follow the same static path, which must be dimensioned for (at least) the sum of the average traffic on the virtual circuits. Instead, pure circuit switching requires that each link supports the worst-case requirements of each circuit using it.

There are three basic packet-switching schemes: store and forward (SAF), virtual cut through (VCT), and WH switching. They are discussed next.

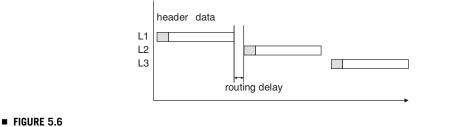

#### SAF switching

SAF switching is the simplest form of packet switching. A packet is sent from one router to the next only when the receiving router has buffer space for the entire packet (Fig. 5.6). Hence, packet transmission cannot stall and the notion of flit is not required (flits are equal to packets). Routers forward a packet only when it has been received in its entirety. As a result, the latency per router and the buffer size are at least equal to the size of the packet. Given that minimizing buffer size is critical in NoCs [89], few NoCs have used this basic technique. In particular, Nostrum [75] uses hotpotato routing [35] where the notions of phit, flit, and packet are conflated (to their link width of 128 bits).

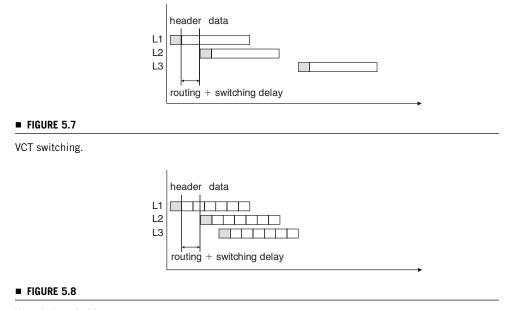

#### VCT switching

VCT switching reduces the per router latency by forwarding the first flit of a packet as soon as space for the entire packet is available in the next router (middle transmission in Fig. 5.7). The other flits then follow without delay. If no space is available, the whole packet is buffered (last transmission in

Wormhole switching.

Fig. 5.7). Buffering requirements of SAF switching and VCT switching are the same, and no NoC has used this basic technique, therefore.

#### WH switching

WH switching improves on VCT switching by reducing the buffer requirements to one flit. This is achieved by forwarding each flit of a packet when there is space for that flit in the receiving router (Fig. 5.8). If no space is available in the next router for the entire packet (as required by VCT switching but not by WH switching), the packet is left strung out over two or more routers. This blocks the link, which results in higher congestion than with SAF and VCT switching. Link blocking can be alleviated by multiplexing virtual links (or virtual channels) on one physical link (cf. Section 5.4.1) [26]. WH switching is also more susceptible to deadlock than SAF and VCT switching due to the newly introduced usage dependencies between links. Virtual channels and/or routing schemes can be used to avoid deadlock (see Section 5.6.2).

Almost all NoCs use WH switching without virtual channels [13, 60] use restricted topologies (usually partial mesh, with some form of dimensionordered routing) to avoid deadlock. SPIN [1] uses a fat tree topology with deflection routing and packet reordering at the receiving network interface, which also avoids routing deadlock. Æthereal's [89] BE service class uses WH switching class and avoids deadlock for any topology through a

combination of turn-prohibition routing and end-to-end flow control [55]. Other approaches [8, 63], use WH switching with virtual channels.

#### 5.4.3 Combinations of Different Switching Techniques

Circuit switching and packet switching have different characteristics that may be useful to combine in a single NoC. With circuit switching it is relatively easy to guarantee bandwidth and latency guarantees for a given set of (virtual) circuits (see Section 5.4.1). Packet switching, on the other hand, has no notion of (virtual) circuits and can therefore support any number of concurrent flows. However, it is hard to give hard bandwidth and latency guarantees.

Virtual circuit switching and packet switching can be combined by allocating (at least one) virtual channel to each class. Guaranteed services are mapped to virtual circuits and BE services to packets. Æthereal [89], Nostrum [75], and Mango [8] use this approach. The first two use TDM and Mango uses "asynchronous latency guarantee" scheduling. Note that although WH switching with very long (infinite) packet lengths also creates virtual circuits [49, 63], but to offer end-to-end performance guarantees the right scheduling discipline is essential.

Basic packet switching is appropriate for very dynamic applications where flows are short lived, change frequently, or very variable in their demands, due to the absence of flow reservations, and set-up and teardown phases. Relatively short messages (synchronization traffic, cache lines, etc.) to many different modules (e.g., distributed memories and caches) makes connection-oriented QoS inappropriate. Connection-less packet switching with BE service class is therefore natural for CMP NoCs. However, to offer assured (guaranteed) service classes, connectionoriented packet switching, based on (TDM) virtual circuits, has been used successfully for ASICs and ASSPs [99].

# 5.5 NoC ADDRESSING AND ROUTING

While the *switching technique*, as discussed in Section 5.4, controls how data is buffered and transported between routers, the routing layer determines the paths over which data follows through the network. Before we do this we briefly describe how the start and end points of the route are indicated through various addressing schemes.

# 5.6 NoC ADDRESSING

In order to route information within the chip unique identifications or addresses must be assigned to each reachable destination. It is important

169

to notice that such destinations may have a hierarchical relationships or layers. For example, a certain modules (e.g., subsystems or tiles) in the chip may have multiple submodules, such as processors and local shared memories. Each processor may execute multiple programs and each program may be composed of multiple tasks and threads. Consequently such an identity can be described as thread 3 of program 7 of processor 1 at module 6.

To hide implementation details logical addresses are often used instead of physical addresses. A single physical address, such as a memory (location) may be known as different logical addresses or vice versa. The former is useful when processors with different memory maps (e.g., 24 or 32 bit addresses, or with different layout) share a single memory to communicate. The latter can be used, for example, for security or virtualization purposes, or to allow different processors to boot from the same fixed address, but with different boot code. The mapping (or translation or resolution) of logical to physical address may be done in software or hardware, distributed or centralized, fixed at design time or configurable at run time [91].

The physical address space in each NoC implementation may be assigned according to the number of different modules (e.g., we use 4 bits for an NoC that has less than 16 modules), the relative location of the module in the NoC (e.g., XY coordinate in a grid or a node name in a fat tree). Logical addresses may relate to functional names (e.g., the external memory interface, a coprocessor unit) or to a global address space (e.g., 16, 24, or 32 bits).

Finally, different flows may belong to different service classes, introduced in the previous Section 5.2. Identifiers may be needed to distinguish flows for QoS purposes, therefore. (Because different flows between the same addresses may below to different flows, separating control and data, for example.) These include identifiers for individual transactions (for reordering), for communication threads (as used e.g., in AXI [2]), and flows/connections [92].

Addressing is discussed in more detail in Chapter 6 on network interfaces (e.g., address translations) and Chapter 7 on NoC programming models (e.g., message passing versus shared memory).

# 5.6.1 NoC Routing

In the following we focus on routing data in NoCs and particularly emphasize the planar mesh topology, which is popular for NoCs. The NoC routing mechanism is responsible for correct and efficient routing of packets (or circuits) that are traversing the network from sources to destinations. The routing protocol deals with resolution of the routing decision made at every router. Unlike traditional communication or interconnection networks, NoCs need not follow rigid networking standards, therefore, a

multiple routing schemes can be evaluated and compared for each NoC implementation. There are several potentially conflicting metrics that need to be balanced:

- Power: minimize the power required to route packets. This means that packets may follow the minimal power path likely to be identical to the traditional shortest distance routing [13, 87]. In certain cases, for example, when DVS is applied in a non-uniform way, each router and link may offer a different packet switching power consumption [95].

- *Area and VLSI resources*: the routing mechanism itself consumes hardware resources like finite state machines, and addresses tables. It potentially also uses NoC bandwidth if routers exchange information.

- *Performance*: reduce the delay and maximize the traffic utilization of the network.

- Robustness to traffic changes: certain routing schemes (e.g., static routing schemes) may perform very well to an expected traffic pattern but poorly to changing traffic patterns. Other schemes (e.g., dynamic routing) may behave better to a larger spectrum of traffic conditions.

Routing schemes can be classified into several different categories. In particular routing can be static or dynamic, distributed or performed at the source, and minimal or non-minimal. We describe each in turn.

#### Static and dynamic routing

The routing decision at every router can be *static* (also called oblivious or deterministic) or *dynamic* (or adaptive).

In a static routing scheme permanent paths from a given source to a given destination are defined and are used regardless of the current state of the network. This routing scheme does not take into account the current load of network links and routers when making routing decisions. Note that static routing may use single path or split the traffic in a predefined way among multiple paths between a source and a destination.

In a dynamic routing scheme, routing decisions are made according to the current state of the network (load, available links). Consequently, the traffic between a source destination changes its route with time.

Static routing is simpler to implement in terms of router logic and interaction between routers. A major advantage of a single path static routing is that all packets with the same source and destination are routed over the same path and can be kept in order. In this case, there is no need to number and reorder the packets at the network interface. Static routing is clearly more appropriate when traffic requirements are steady and known ahead of time, and therefore is preferable for NoCs for ASICs or ASSPs. Dynamic or adaptive routing may utilize alternative paths when certain directions become congested and therefore have the potential of supporting more traffic using the same network topology. Consequently it may be preferable in irregular and unpredictable traffic conditions, which are more common to the CMP NoCs.

#### Distributed and source routing

Routing techniques (both static and dynamic) can be further classified according to where the routing information is held and where routing decisions are made.

In *distributed* routing, each packet carries the destination address, for example the XY coordinates of the destination router or network interface, or a module number. The routing decision is implemented in each router either by looking up the destination addresses in a routing table or by executing a hardware routing function [14]. Using this method, each network router contains a predefined routing function whose input is the destination address of the packet and its output is the routing decision. When the packet arrives at the input port of the router, its output port is looked up in the table or calculated by the routing logic according to the destination address carried by the packet. Note that in order to reduce routing table space a specific distributed routing technique may restrict its supported network topology, the type of routes that can be defined and the naming convention of network destination. A very common example in NoCs is the XY routing (also termed dimension routing [24]) for mesh networks where destinations are named after their geographical (XY) coordinates and the intermediate routing function is limited to the comparison between the router address and the destination address. Interval routing [11] suggests a similar reduced table space methodology for general topology networks.

In *source routing* the pre-computed routing tables are stored in the network interface at the system modules. When a source router (network interface) transmits a packet, it looks up the source routing information according to the destination address at the source routing table and includes it in the header of the packet. Each packet carries in its header the routing choices for each hop along its path (typically the output link identity). When the packet arrives at a network router, its next routing output port is extracted from the header routing field. The routing field is then shifted in order to expose the relevant routing choice for the next router on its path. In comparison to distributed routing, source routing does not need any intermediate routing tables or functions, it may also eliminate the destination address field required in distributed. On the other hand, it requires a source route header in the packet header (whose size increases with the path length) and requires additional routing tables with specific entries for each source (these can be located in the source network interface or in a centralized pool). Æthereal uses source routing [44].

While distributed routing and source routing describe the way packets and router interact to perform intermediate routing decisions, both schemes leave a full degree of freedom in deciding on the selection of the (static) packet routes. Most distributed routing designs make a conscious limitation on the selected routes. In order to reduce the amount of logic required, routes are based only on the destination address rather than on the source and destination address pair.

#### Minimal and non-minimal routing

A final classification criterion distinguishes between *minimal* and *nonminimal* distance routing. In contrast to traditional interconnection networks, the additional power consumption introduced by non-minimal routes may be prohibitively expensive in an NoC [57]. Note that in heterogeneous NoCs where links between routers are of different speed and length, minimal power routing is not equivalent to a minimal link hop routing [12].

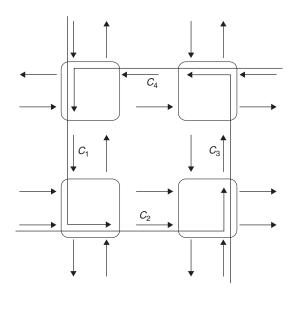

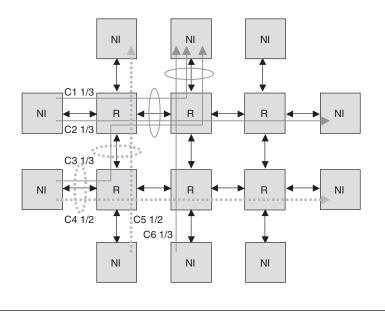

# 5.6.2 Deadlock

The major constraint for any routing algorithm is assuring the freedom from *deadlock*. In packet switching networks whenever a packet or flit is transferred between neighboring routers, it releases a buffer at the transmitter and occupies a previously free buffer at the receiver. Consequently, such a transfer requires the availability of a free buffer at the receiver, or the flit is held (in a lossless network), due to link-level flow control, until such a buffer is freed at the receiver. Deadlock occurs when one or more packets in the network become blocked and stay blocked for an indefinite time, waiting for an event that cannot happen. A typical example, as depicted in Fig. 5.9 [81], is a situation where four packets are routed in a circular manner between the routers in a square mesh. The packet occupying channel  $c_1$  is waiting for  $c_2$  and that channel is allocated to a packet that wants to use  $c_3$ . That channel in turn is held by a packet that is requesting  $c_4$  and the packet on this channel completes the circle by waiting for  $c_1$ . No packet can advance since the required resource, in this case the channel, is already held by another packet and will never be released.

While WH switching is the prevalent switching technique for NoCs (due to its relatively small buffering requirements), it is prone to suffer from deadlocks. Since only the header flit carries routing information all flits belonging to the same packet must be contiguous and cannot be interleaved with flits belonging to other packets [29]. If a flit is blocked due to busy resources all the trailing flits of that packet will also be stopped and keep blocking the resources they occupy in terms of channels and buffers. This can result in chained blocking [26] where the resources of a blocked packet again causes other packets to block, a property that makes WH routing very susceptible to deadlock [29, 36].

#### ■ FIGURE 5.9

Deadlocked scenario with packets waiting for channels in a cyclic manner.

#### **Deadlock avoidance**

The prominent strategy for dealing with deadlock is avoidance and most deadlock-free routing algorithms are deduced by the strategy of [29, 36]: (1) choose a particular routing algorithm, (2) check whether this algorithm is deadlock free, and (3) if needed, add hardware resources or restrict routing to make the algorithm deadlock free.

Deadlock freedom is analyzed by building a dependency graph of the shared network resources. Whenever a packet is holding a resource while requesting another there is a *dependency* between them and if this dependency graph is cyclic then we have a circular wait. Analysis of the graph can be done statically, with all possible dependencies represented in the graph, or dynamically, with the graph reflecting the current state of the system. Static analysis is unnecessarily pessimistic since dependencies that are mutually exclusive can be part of a cycle that never occurs at run time. However, the big advantage with static analysis is that it can be done beforehand and thus detach this computationally intensive problem from the actual system.<sup>1</sup> Thus, deadlock is usually avoided by employing a restrictive routing algorithm.

<sup>&</sup>lt;sup>1</sup> Much research has been focused on distributed cycle detection mechanisms that allow for progressive deadlock recovery based on only local information while keeping recovery overhead to a minimum [19, 20, 72].

#### FIGURE 5.10

Channel dependency graph of a mesh in which the routers use edge buffers. (a) For one router and (b) for the entire mesh.

Deadlock freedom in SAF and VCT networks, which are identical from a deadlock perspective [29], is proved using a buffer-ordering technique of Ref. [51]. In a WH-switched network blocked messages remain in the network and hence continue to occupy the links until contention is resolved. Therefore, we cannot use restrictions in buffer allocation to prevent deadlock, but must instead restrict routing over the communication channels, be they physical or virtual.

The dependencies of a WH-switched network are captured in a *channel dependency graph* [29]. Fig. 5.10 illustrates the channel dependencies of a minuscule network. With a fully dynamic routing function every input channel has the possibility of forwarding a packet to any output channel and the channel dependency graph of a single router thus looks as shown in Fig. 5.10(a). The graph is obviously acyclic since all the input and output ports of the router are dangling. In Fig. 5.10(b) we see the corresponding graph for a simple two-by-two mesh and this figure contains numerous cycles. There is thus a risk of channel deadlock in the network.

Dally et al. [29] propose a necessary and sufficient condition for deadlock freedom in the case of a static routing function. This proof technique is extended in Refs [27, 70] to also cover dynamic routing.

Introducing virtual channels increases the degrees of freedom in alleviating restrictions in the choice of channels (see Section 5.4.1) [40] and can aid both in avoiding deadlock as well as increasing network throughput by reducing the effects of chained blocking [26]. By dissociating the buffers (associated with channels) from the actual physical channels, a blocked packet in one virtual channel does not preclude packets residing on other virtual channels [77] as depicted in Fig. 5.11.

The problem of deadlocks in a WH NoC can be alleviated by the use of multiple virtual channels. The idea is that more buffers can be allocated in the receiver size to different flows (e.g., a Virtual Channel per destination). However, the number of Virtual Channels that are required

5.6 NoC Addressing

#### FIGURE 5.11

A packet  $p_2$  is blocked by a previous packet  $p_1$  and is occupying the physical channel between the routers. Packet  $p_3$  that follows  $p_2$  is allowed to proceed and pass  $p_2$  by using the buffers associated with another virtual channel.

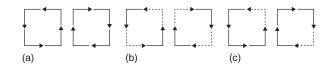

to completely solve the deadlock problem for any routing scheme, is large [28, 33] and therefore costly in terms of VLSI resources. There are general mechanisms for avoiding deadlocks by restricting the routing algorithms. Glass and Ni [40] call a specific pair of input-output links around a router as a turn and introduce several deadlock-free routing schemes based on *turn prohibition*. Enough turns are prohibited to break all dependency cycles while still maintaining connectivity between every pair of routers. The Æthereal BE service class uses the turn model for routing on arbitrary topologies [54]. The most simplistic approach to turn prohibition is the well-known dimension-ordered routing. It is a static and minimal distance routing algorithm where a packet is routed in one dimension at a time, finding the correct coordinate in each dimension before continuing with the next. In a two-dimensional mesh this method is known as XY routing and is very popular due to its simplicity. When a packet is sent it will be forwarded in the X dimension until it reaches the X coordinate of the destination; only then is it forwarded in the Y dimension until it reaches its goal.

An illustration of the turn model in a two-dimensional mesh is shown in Fig. 5.12. There are eight possible turns that form two cycles if no turns are prohibited. With the static XY routing four of the turns are prohibited and it is clear that no cycles can be formed from the remaining turns. It is not necessary to prohibit this many turns to guarantee deadlock freedom. The *west-first* routing algorithm [41], illustrated in Fig. 5.12(c), prohibits only two of the eight turns and manages to break all cycles thereby constituting a deadlock-free routing algorithm.

Many contemporary NoC proposals based on a regular mesh topology have implemented the above dimension-order (XY) based routing. It is shown in Refs [13, 52] that this may cause a significant imbalance in the traffic utilization of the mesh links, even when traffic requirements are symmetric. When traffic patterns are known ahead of time (for ASICs), this can be dealt with using NoCs with asymmetric link capacities such as QNoC [13, 52], where each link capacity is planned according to its expected load. This eliminates the need for an expensive implementation

#### FIGURE 5.12

Illustration of turn prohibition in two-dimensional mesh. (a) Unprohibited mesh with two cycles, (b) four prohibited turns of XY routing, and (c) two prohibited turns of west-first routing.

#### ■ FIGURE 5.13

SoC modules interconnected by an irregular mesh NoC.

of an dynamic load balance routing that requires the reordering of packets at the network interfaces. A simple alternative to link capacity planning is to use a combination of alternatively (or randomly) choosing between XY and YX routing as described in Refs [59, 94] that is close to optimal in terms of maximum utilization in a homogenous mesh. Therefore, the "toggle" XY–YX routing above better suits a FPGA type device where the links between the routers cannot be customized ahead of time for specific loads [39]. While other balanced static routing schemes (also termed oblivious routing [71]) were introduced for mesh-based interconnection networks (and can be implemented using source routing), they usually require too much hardware to be used in a low-budget NoC environment.

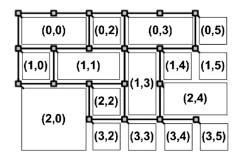

Another problem which is related to low-cost static routing is how to cope with irregular meshed NoCs that result from module size variability and the need to physically separate between the modules internals and the NoC infrastructure, as illustrated in Fig. 5.13.

Packet routing in irregular meshes resembles routing in a labyrinth, since missing links may lead to a dead end. Therefore, a simple XY or XY-YX "toggle" scheme cannot be employed and different routing techniques need to be applied. In off-chip networks, routing in irregular topologies is typically accomplished using routing tables located in routers or in sources. Routing table size and the corresponding power and area costs grow with the network size. Moreover, the time required to access

each table, which affects NoC performance, depends on its size and thus on the network size.

Reference [14] develops hardware-efficient routing techniques that reduce the VLSI cost of routing in irregular mesh topology NoCs. The techniques are based on a combination of a fixed routing function (such as "route XY" or "don't turn") and reduced routing tables for both distributed and source routing approaches. The entries in the reduced routing tables are created only for destinations whose routing decisions differ from the output of the default routing function. Random simulations of different topologies and flow scenarios are used for comparing and estimating the VLSI cost savings obtained by different algorithms. This mechanism is found to be superior (around five times lower cost) to the traditional source routing and routing table-based techniques.

# 5.6.3 NoC Dynamic Routing Schemes<sup>2</sup>

Dynamic routing is an efficient alternative to balance the traffic load over a given NoC where the NoC traffic is unpredictable or changes with time (e.g., the CMP NoC type). Note that when a source destination traffic is split over multiple paths, packets may arrive out of order and re-sequencing buffers at the destination may be required. The simplest method of dynamic routing is termed *deflection routing* or *hot-potato* routing. It was suggested for metropolitan networks [73], optical burst networks [15], and interconnection networks [35]. In this scheme, when a packet enters a router it will be sent toward a preferred output port according to a routing table or a routing function as described above. However, if the preferred port is busy (blocked by a backpressure from a neighboring router, or captured by another packet) an alternative port will be selected. Here the router has no additional buffers in which to store the packets before they are moved, and each packet is constantly transferred until it reaches its final destination. The packet is bounced around like a "hot potato," sometimes moving further away from its destination because it has to keep moving through the network. This is in contrast to SAF switching where the network allows temporary storage at intermediate locations (Section 5.4.2). Deadlocks cannot happen in deflection routing when the number of input and output ports of a switch are identical and new local packets are not allowed in when all inputs are busy. It is guaranteed that any packet in a router will be transferred in the next cycle to any of the output ports and therefore the router can receive a new packet over all its inputs from neighboring routers (so no backpressure is sent among routers). *Livelocks* may happen in deflection routing and needs to be resolved. A livelock situation happens when a packet is sent

<sup>&</sup>lt;sup>2</sup> We acknowledge contributions from Andreas Hansson [53, 54] for this section.

over and over and never reaches its final destination. Simple priority rules can resolve it [17].

While there is a broad literature on the use of deflection routing in various networks, one may question the impact of this scheme on the NoC power consumption due to the long routes packets may take in the network. However, the benefits of an dynamic routing scheme for the CMP model may overcome the disadvantages. First, deflection routing automatically spreads traffic to alternate routes when primary routes are in demand. Second, routes can be selected according to profitability [109] where routes that move packets closer to the destination are favorable over paths that lead packets away from it. Finally, in the NoC environment, the backpressure from neighboring routers may be more effective than in off-chip networks due to the relative proximity of routers to each other. Nilsson et al. [83] suggest avoiding excessive oscillations by exchanging "stress values" among neighboring routers. Packets are routed away from "stressed areas." Ye et al. [109] leverage the previous idea and suggests a contention-look-ahead routing based on flits in a WH network.

Several more dynamic routing technologies have been suggested to NoCs. An interesting technique that switches between the XY and the YX in an dynamic way is described in Ref. [59]. Gossip-based routing which is based on a broadcast of the information to all destinations is suggested in Refs [17, 34].

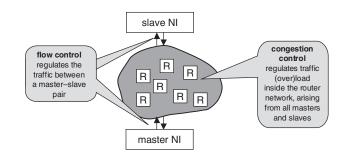

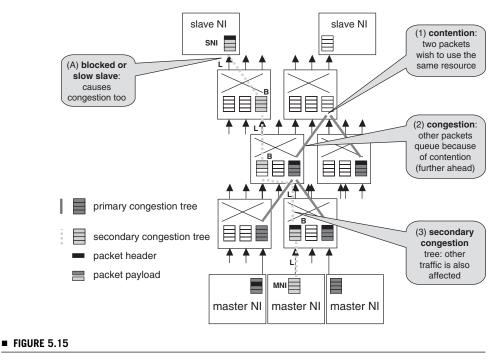

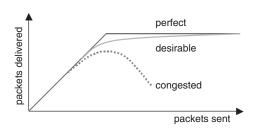

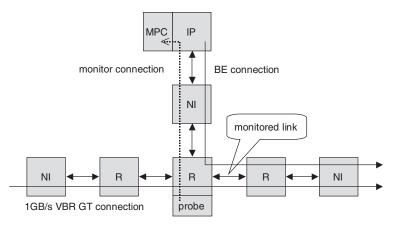

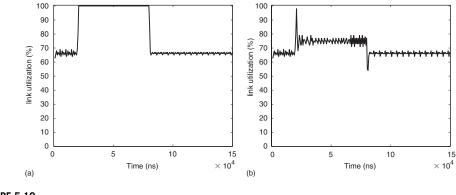

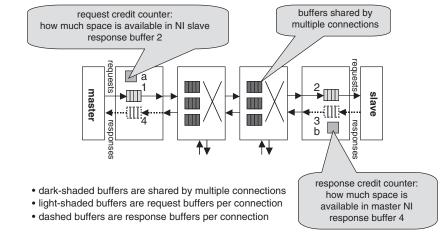

SPIN [49] uses dynamic routing in a fat tree topology. In routing from one module to another, any path to a common ancestor in the tree may be taken. A unique path then exists from that ancestor to the destination module. Although all paths between a pair of modules have the same length, delays may be different on different paths due to congestion and re-sequencing buffers are necessary at the receiver network interface.